# PhD Thesis

# Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

## Université Polytechnique Hauts-de-France Discipline : **Computer Engineering**

Presented and defended by : MOHAMED AYOUB NEGGAZ. On Mai 28th, 2020, à Valenciennes.

École doctorale : Sciences Pour l'Ingénieur (ED SPI 072). Laboratoire : LAMIH UMR CNRS 8201.

## HARDWARE ACCELERATORS FOR MACHINE LEARNING APPLICATIONS. CASE STUDY: AUTONOMOUS VEHICLES

| Jury president<br>Reporters |   | Frederic Pétrot.<br>Andreas Herkersdorf. | Professor, Université Grenoble Alpes.<br>Professor, Technische Universität München. |

|-----------------------------|---|------------------------------------------|-------------------------------------------------------------------------------------|

| Examiner                    |   | Frederic Pétrot.                         | Professor, Université Grenoble Alpes.                                               |

|                             |   | CATHERINE DEZAN.                         | Professor, Université de Brest.                                                     |

| Thesis directors            | : | Smail Niar.                              | Professor, UPHF.                                                                    |

|                             |   | Fadi Kurdahi.                            | Professor, University of California, Irvine.                                        |

| Thesis co-supervisor        | : | Ihsen Alouani.                           | Professor, UPHF.                                                                    |

May 2020

## Thése de doctorat

# Pour l'obtention du grade de Docteur de

## l'Université Polytechnique Hauts-de-France Discipline : Informatique

Présentée et soutenue par : MOHAMED AYOUB NEGGAZ. Le 28 Mai 2020, à Valenciennes.

Laboratoire

École doctorale : Sciences Pour l'Ingénieur (ED SPI 072).

: LAMIH UMR CNRS 8201.

## ACCÉLERATEURS MATÉRIELS POUR L'INTÉLLIGENCE ARTIFICIELLE. ÉTUDE DE CAS: VOITURES AUTONOMES

| Président du jury<br>Rapporteurs    |   | Frederic Pétrot.<br>Andreas Herkersdorf.<br>Frederic Pétrot. | Professeur, Université Grenoble Alpes.<br>Professeur, Technische Universität München.<br>Professeur, Université Grenoble Alpes. |

|-------------------------------------|---|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Examinateurs<br>Directeurs de thèse |   | Catherine Dezan.<br>Smail Niar.<br>Fadi Kurdahi.             | Professeure, Université de Brest.<br>Professeur, UPHF.<br>Professeur, University of California, Irvine.                         |

| Co-encadrant de thèse               | : | Ihsen Alouani.                                               | Maître de Conférences, UPHF.                                                                                                    |

Mai 2020

## Résumé

Depuis les débuts du défi DARPA, la conception de voitures autonomes suscite un intérêt croissant. Cet intérêt grandit encore plus avec les récents succès des algorithmes d'apprentissage automatique dans les tâches de perception. Bien que la précision de ces algorithmes soit irremplaçable, il est très difficile d'exploiter leur potentiel. Les contraintes en temps réel ainsi que les problèmes de fiabilité alourdissent le fardeau de la conception de plateformes matériels efficaces. Nous discutons les différentes implémentations et techniques d'optimisation de ces plateformes dans ce travail. Nous abordons le problème de ces accélérateurs sous deux perspectives : performances et fiabilité. Nous proposons deux techniques d'accélération qui optimisent l'utilisation du temps et des ressources. Sur le volet fiabilité, nous étudions la résilience des algorithmes de Machine Learning face aux fautes matérielles. Nous proposons un outil qui indique si ces algorithmes sont suffisamment fiables pour être employés dans des systèmes critiques avec de fortes critères sécuritaire ou non. Un accélérateur sur processeur associatif résistif est présenté. Cet accélérateur atteint des performances élevées en raison de sa conception en mémoire qui remédie au goulot d'étranglement de la mémoire présent dans la plupart des algorithmes d'apprentissage automatique. Quant à l'approche de multiplication constante, nous avons ouvert la porte à une nouvelle catégorie d'optimisations en concevant des accélérateurs spécifiques aux instances. Les résultats obtenus surpassent les techniques les plus récentes en termes de temps d'exécution et d'utilisation des ressources. Combinés à l'étude de fiabilité que nous avons menée, les systèmes ou la sécurité est de priorité peuvent profiter de ces accélérateurs sans compromettre cette dernière.

Mots Clés Voitures Autonomes, Intélligence Artificielle, FPGA, GPU, ASIC, CNN, Systèmes Embarqués, Fiabilité.

### Abstract

Since the early days of the DARPA challenge, the design of self-driving cars is catching increasing interest. This interest is growing even more with the recent successes of Machine Learning algorithms in perception tasks. While the accuracy of these algorithms is irreplaceable, it is very challenging to harness their potential. Real-time constraints as well as reliability issues heighten the burden of designing efficient platforms.

We discuss the different implementations and optimization techniques in this work. We tackle the problem of these accelerators from two perspectives: performance and reliability. We propose two acceleration techniques that optimize time and resource usage. On reliability, we study the resilience of Machine Learning algorithms. We propose a tool that gives insights whether these algorithms are reliable enough for safety critical systems or not.

The Resistive Associative Processor accelerator achieves high performance due to its in-memory design which remedies the memory bottleneck present in most Machine Learning algorithms. As for the constant multiplication approach, we opened the door for a new category of optimizations by designing instance specific accelerators. The obtained results outperforms the most recent techniques in terms of execution time and resource usage. Combined with the reliability study we conducted, safety-critical systems can profit from these accelerators without compromising its security.

**Keywords** Autonomous Vehicles, Artificial Intelligence, FPGA, GPU, ASIC, CNN, Embedded Systems, Reliability.

# Acknowledgments

To my wife, Amina, my son, Isaac, and my sister, Maria.

# Contents

| 1 | Mo  | tivations and Thesis Objectives                 | 13 |

|---|-----|-------------------------------------------------|----|

|   | 1.1 | Deep Learning for Autonomous Vehicles           | 14 |

|   | 1.2 | Aim of Thesis                                   | 15 |

|   | 1.3 | Main Contributions                              | 17 |

|   | 1.4 | Outline                                         | 18 |

| 2 | Ma  | chine Learning: A Review                        | 21 |

|   | 2.1 | Artificial Intelligence and Machine Learning    | 24 |

|   | 2.2 | Motivations Behind Machine Learning             | 25 |

|   | 2.3 | How it works?                                   | 26 |

|   | 2.4 | Datasets                                        | 31 |

|   | 2.5 | Common CNN Architectures                        | 31 |

|   | 2.6 | CNN Profiling                                   | 33 |

| 3 | Aut | conomous Driving Systems                        | 37 |

|   | 3.1 | Driver-Assistance Systems                       | 38 |

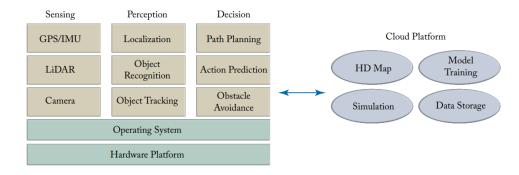

|   | 3.2 | Autonomous Driving System                       | 39 |

|   | 3.3 |                                                 | 42 |

|   | 3.4 | Autonomous Vehicle Constraints                  | 45 |

|   | 3.5 | Simulators                                      | 46 |

|   | 3.6 | Frameworks for Autonomous Driving               | 46 |

|   | 3.7 | ADS Design Example                              | 48 |

|   | 3.8 | Summary                                         | 52 |

| 4 | Hai | dware Platforms for Machine Learning            | 55 |

|   | 4.1 | CNN Optimization Techniques                     | 56 |

|   | 4.2 | CPU                                             | 61 |

|   | 4.3 | GPU                                             | 67 |

|   | 4.4 | FPGA                                            | 72 |

|   | 4.5 | ASIC                                            | 77 |

|   | 4.6 | General Conclusion                              | 81 |

| 5 | Des | ign for Performance: On Associative Processors  | 85 |

|   | 5.1 | Motivations                                     | 86 |

|   | 5.2 | Hardware Accelerators for Matrix Multiplication | 87 |

|   | 5.3 | Resistive Associative Processor                 | 89 |

|   | 5.4 |                                                 | 93 |

|   | 5.5 | Experimental Results                            | 95 |

|   | 5.6 | Contributions and Guidelines                    | 99 |

| 6 | $\mathbf{Des}$                    | ign for Performance: On Constant Multiplication 10                                                                                                                     | <b>3</b>                                     |

|---|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 6.1                               | Motivations                                                                                                                                                            | )4                                           |

|   | 6.2                               | Background                                                                                                                                                             | )5                                           |

|   | 6.3                               | Related works on complexity reduction                                                                                                                                  | )5                                           |

|   | 6.4                               | Proposed Approach                                                                                                                                                      | )8                                           |

|   | 6.5                               | Theoretical Performance Study                                                                                                                                          | .1                                           |

|   | 6.6                               | Circuit-Level Experimental Results                                                                                                                                     | 4                                            |

|   | 6.7                               | RTL-Level Experimental Results                                                                                                                                         |                                              |

|   | 6.8                               | Discussion                                                                                                                                                             | 9                                            |

|   | 6.9                               | Contributions and Guidelines                                                                                                                                           | 20                                           |

|   |                                   |                                                                                                                                                                        |                                              |

| 7 | Des                               | ign for Reliability: A Fault Injection Study 12                                                                                                                        | 1                                            |

| 7 | <b>Des</b><br>7.1                 | -8                                                                                                                                                                     | _                                            |

| 7 |                                   | Motivations                                                                                                                                                            | 22                                           |

| 7 | 7.1                               | Motivations       12         Soft Errors Primer       12                                                                                                               | 22<br>23                                     |

| 7 | $7.1 \\ 7.2$                      | Motivations       12         Soft Errors Primer       12         Fault Injection in Embedded Systems       12                                                          | 22<br>23<br>23                               |

| 7 | $7.1 \\ 7.2 \\ 7.3$               | Motivations       12         Soft Errors Primer       12                                                                                                               | 22<br>23<br>23<br>24                         |

| 8 | $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5$ | Motivations       12         Soft Errors Primer       12         Fault Injection in Embedded Systems       12         Impact of Soft Errors on CNN's Accuracy       12 | 22<br>23<br>23<br>24<br>82                   |

|   | $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5$ | Motivations12Soft Errors Primer12Fault Injection in Embedded Systems12Impact of Soft Errors on CNN's Accuracy12CNN Fault Injector13                                    | 22<br>23<br>23<br>24<br>22<br>23<br>24<br>22 |

# List of Figures

| 1.1                                       | Comparison of fatalities caused by accidents in different transportation<br>modes, data reported by the US' NTSB                              |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                       | Sensor modules for each automation level from [251]                                                                                           |

| 1.2                                       | The reading dependencies between chapters. Chapters with the black                                                                            |

| 1.0                                       | document icon in the top right corner contain details of at least one                                                                         |

|                                           | peer-reviewed publication                                                                                                                     |

| 2.1                                       | Moore's Law describing how the performance of compute platforms                                                                               |

|                                           | evolve with time                                                                                                                              |

| 2.2                                       | Timeline of the advances in artificial intelligence and the rise of ma-                                                                       |

|                                           | chine learning                                                                                                                                |

| 2.3                                       | Classification of Machine Learning (ML) algorithms and sub-categories<br>of each class with some example algorithms are given at the nodes of |

|                                           | each sub-category                                                                                                                             |

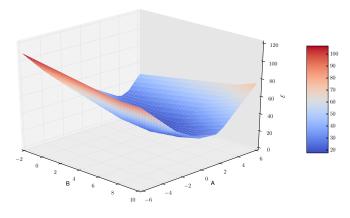

| 2.4                                       | Distribution of the error function $\mathcal{E}$ from Equation 2.3                                                                            |

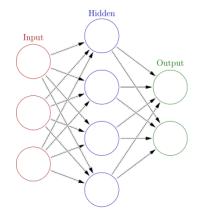

| 2.5                                       | Architecture of an Artificial Neural Network                                                                                                  |

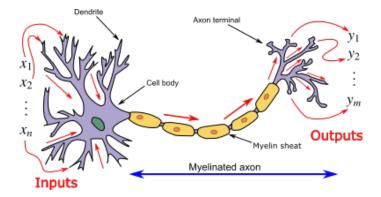

| 2.6                                       | Analogy between a neuron in the human brain and artificial neurons 29                                                                         |

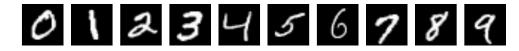

| 2.7                                       | Subset of MNIST images                                                                                                                        |

| 2.8                                       | Subset of CIFAR-10 images                                                                                                                     |

| 2.9                                       | Subset of IMAGENET images                                                                                                                     |

|                                           | Architecture of LeNet5                                                                                                                        |

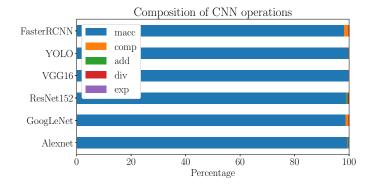

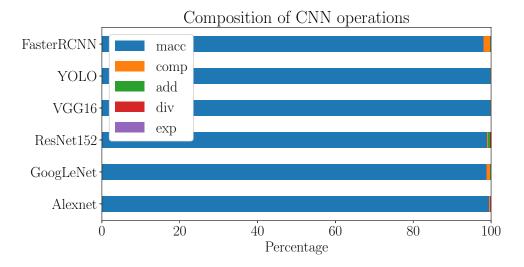

| 2.11                                      | Percentage of Multiply and Accumulate (macc), comparison (comp), addition (add), division (div) and exponent (exp) operations for dif-        |

| 0.40                                      | ferent networks                                                                                                                               |

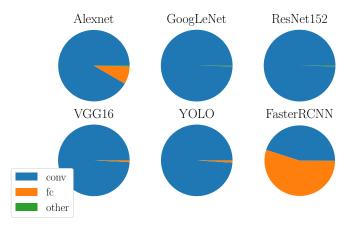

| 2.12                                      | Distribution of MACC operations over different network layers 35                                                                              |

| 3.1                                       | The six levels of driving automation as defined by SAE International in J3016                                                                 |

| 3.2                                       | Autonomous driving system architecture overview from [140] 39                                                                                 |

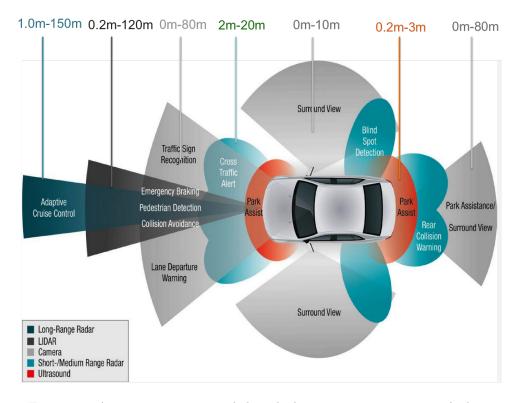

| 3.3                                       | Automotive sensors and their deployment on autonomous vehicles 40                                                                             |

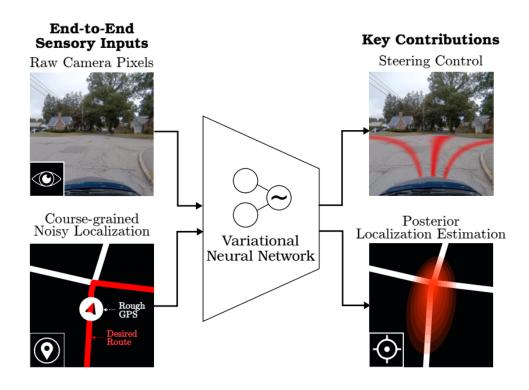

| 3.4                                       | Localization, navigation and control using a neural network from [10]. 41                                                                     |

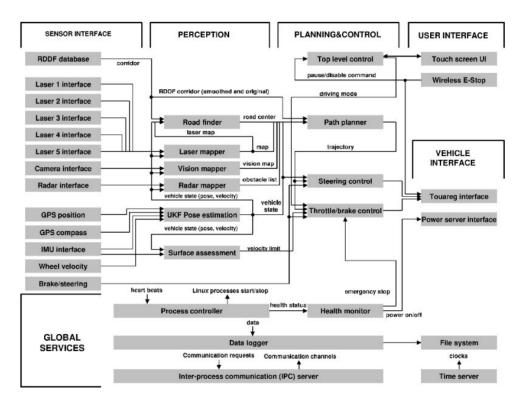

| 3.5                                       | Flowchart of Stanley software system from [27]                                                                                                |

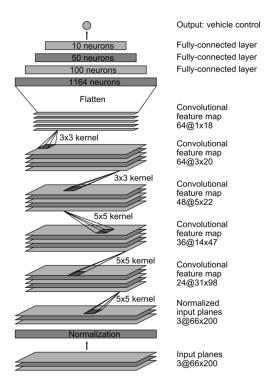

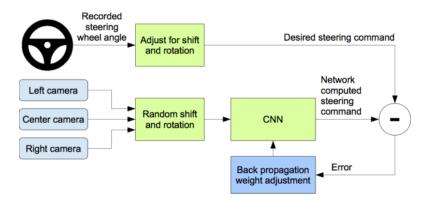

| 3.6                                       | Architecture of the end-to-end system from NVIDIA's DAVE-2 48                                                                                 |

| 3.7                                       | Training of the neural network used in NVIDIA's self-driving car $48$                                                                         |

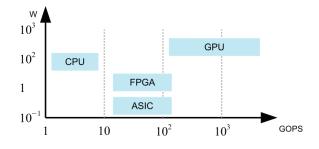

| 3.8                                       | Comparison between different platforms                                                                                                        |

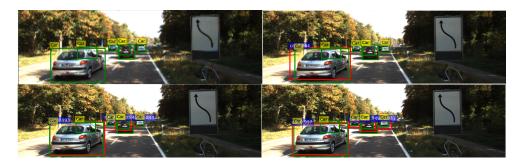

| 3.9                                       | Evolution of detection when increasing the input resolution. From top-                                                                        |

|                                           | left to bottom-right: detection with 20%, 40%, 80% and 100% original size                                                                     |

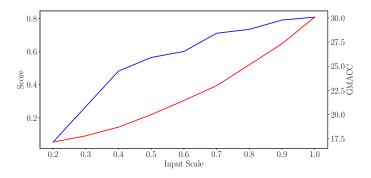

| 3.10                                      | Impact of input size on network size (billion multiply-accumulates) and                                                                       |

|                                           | accuracy (compared to ground-truth                                                                                                            |

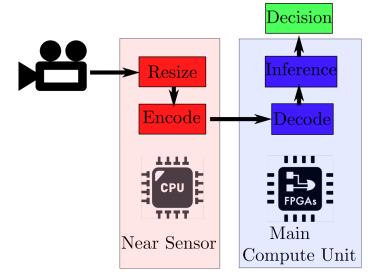

| 3.11                                      | Architecture of the proposed encode/decode pipeline                                                                                           |

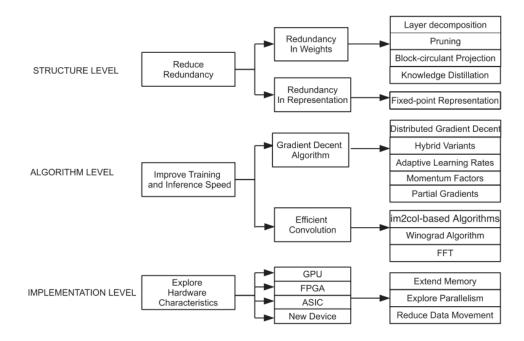

| $\begin{array}{c} 4.1 \\ 4.2 \end{array}$ | Taxonomy of CNN acceleration methods from [262]                                                                                               |

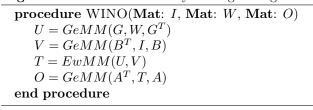

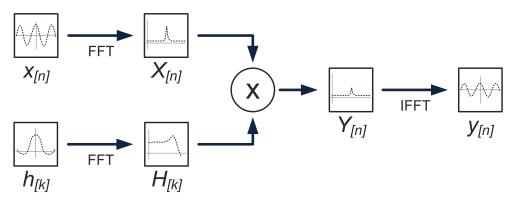

| 4.3  | The FFT transformation of the convolution operation between an in-<br>puts $X$ and a filter window $h$ . The output $y$ is obtained by applying                                                                                                                                                                      |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | an inverse FFT to the dot product of their FFT transformations                                                                                                                                                                                                                                                       | 59 |

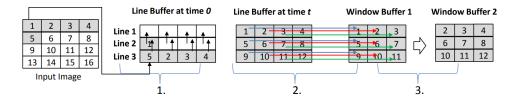

| 4.4  | Line buffer and window buffer example for convolution operation from [149]                                                                                                                                                                                                                                           | 60 |

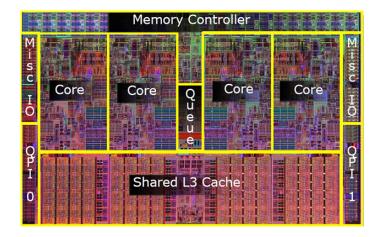

| 4.5  | Architecture of Intel's processor Core-i7.                                                                                                                                                                                                                                                                           | 62 |

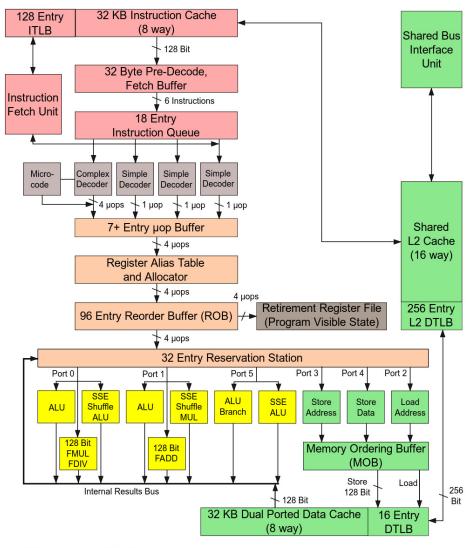

| 4.6  | Intel Core micro-architecture.                                                                                                                                                                                                                                                                                       | 63 |

| 4.7  | Example definition of network described in Caffe's <i>prototxt</i> format on                                                                                                                                                                                                                                         | 00 |

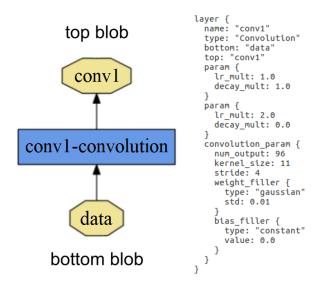

| 4.1  | the right. The equivalent architecture of the network is on the left. It has a single convolution layer where data is stored in <i>blobs</i> . A <i>blob</i> is Caffe's notation for a vector of elements.                                                                                                           | 65 |

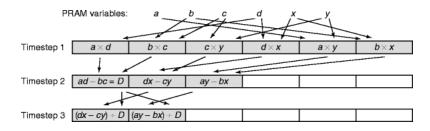

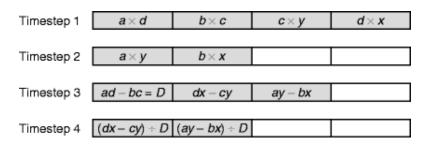

| 4.8  | Parallel solution for a system of two equations with two unknowns.<br>The considered processor has 6 cores. Each column represent one core<br>and each row shows the instruction to be executed in the given core at<br>a given time.                                                                                | 66 |

| 4.9  | Solution to the system from 4.8 with 4 cores for $u$ and $v$ . The final values should be: $u = \frac{dx - cy}{ad - bc}$ and $v = \frac{ay - bx}{ad - bc}$ .                                                                                                                                                         | 66 |

| 4.10 | NVIDIA TU102 Diagram.                                                                                                                                                                                                                                                                                                | 68 |

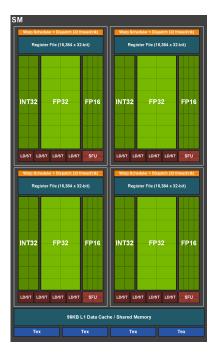

|      | Architecture of the Streaming Multiprocessor (SM) in the NVIDIA TU102.                                                                                                                                                                                                                                               | 69 |

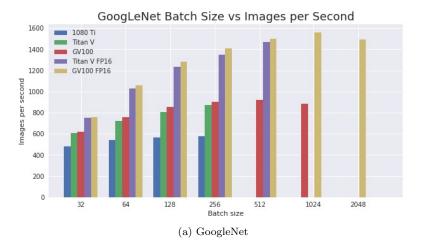

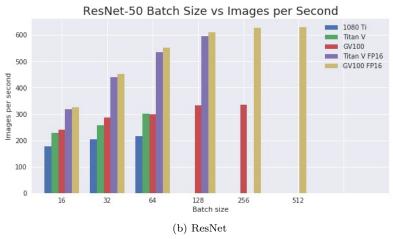

| 4.12 | The impact of increasing the batch size on the performance measured<br>as the number of processed images per second for CNN inference. The<br>missing bars at high batch sizes represent a GPU failure due to its<br>memory size.                                                                                    | 70 |

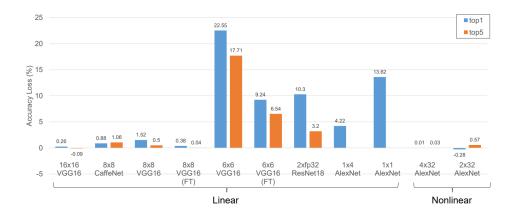

| 4.13 | Comparison between different quantization methods from [75], [83], [131], [185], [270] and [271]. The quantization configuration is expressed as (weight bit-width) $\times$ (activation bit-width). The "(FT)"                                                                                                      |    |

|      | denotes that the network is fine-tuned after a linear quantization                                                                                                                                                                                                                                                   | 74 |

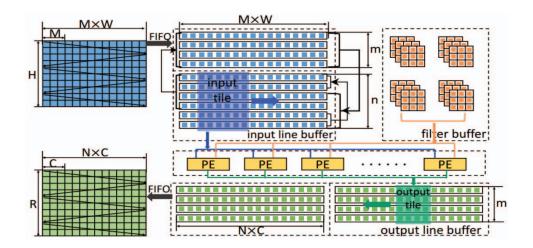

| 4.14 | Generic data paths of FPGA-based CNN accelerators from [3]                                                                                                                                                                                                                                                           | 75 |

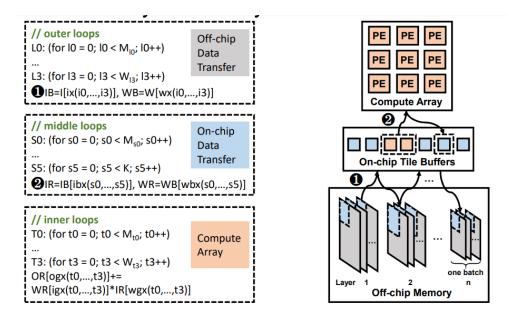

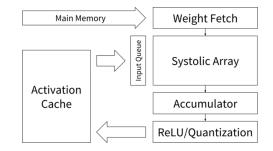

| 4.15 | Standard dataflow of CNN/DNN accelerators                                                                                                                                                                                                                                                                            | 76 |

| 4.16 | Architecture overview of the accelerator from [143]                                                                                                                                                                                                                                                                  | 77 |

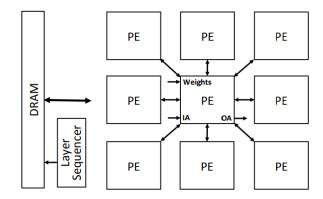

| 4.17 | Architecture of the ASIC proposed in [175].                                                                                                                                                                                                                                                                          | 78 |

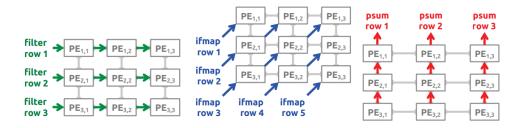

| 4.18 | Dataflow of a single PE of Eyeriss, the accelerator from [36]. From left to right, in green is the flow of weights, in red the flow of input feature maps and finally in red the flow of partial sums.                                                                                                               | 79 |

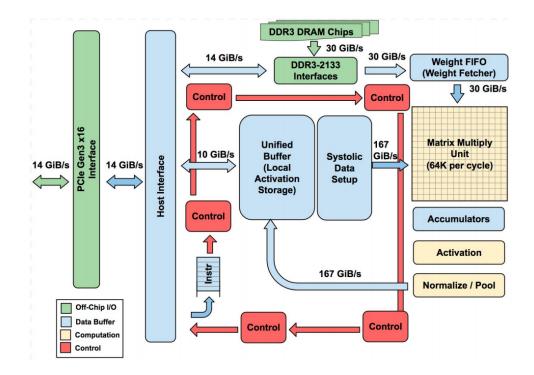

| 4.19 | Architecture of the TPU from [111].                                                                                                                                                                                                                                                                                  | 80 |

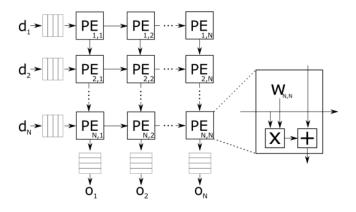

|      | Architecture of a Systolic Array                                                                                                                                                                                                                                                                                     | 80 |

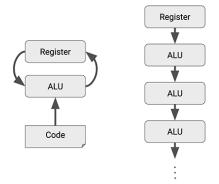

|      | The simplified architecture of a CPU core on the left. The connections between ALUs in a TPU is on the right.                                                                                                                                                                                                        | 81 |

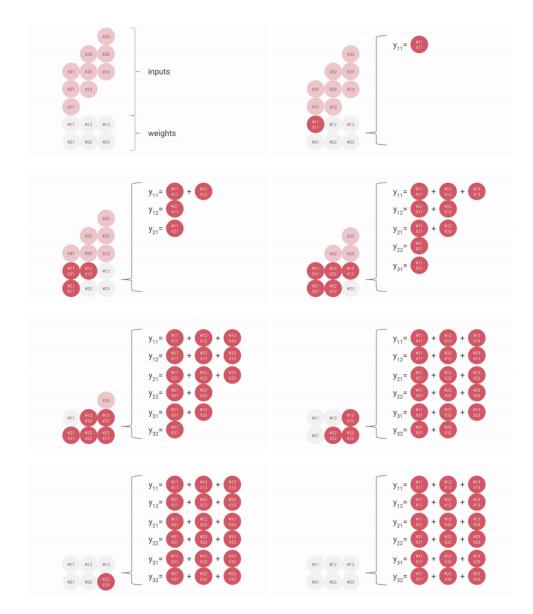

| 4.22 | From top left to bottom right, the execution flow of a $3 \times 3$ input feature<br>map and a $3 \times 2$ weight matrix. Weights are passed to the execution<br>units colored in gray. The input, in light red, is then streamed through<br>the systolic array. The computed outputs is shown on the right of each |    |

|      | figure                                                                                                                                                                                                                                                                                                               | 82 |

|      | Overall architecture of the accelerator from [118] Comparison from [137] of various hardware accelerators in terms of                                                                                                                                                                                                | 83 |

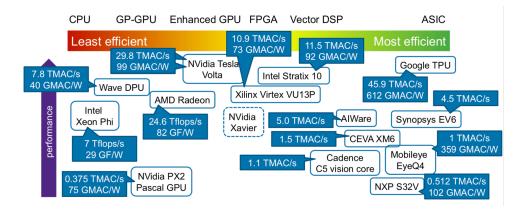

|      | energy efficiency, measured as GMACs per Watts, and performance, measured as TMACs/Tflops per second.                                                                                                                                                                                                                | 83 |

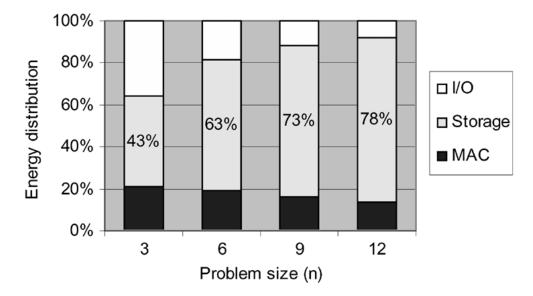

| 5.1  | Energy distribution of a matrix multiplication design proposed in [125]. With large instances, storage tends to dominate energy consumption.                                                                                                                                                                         | 87 |

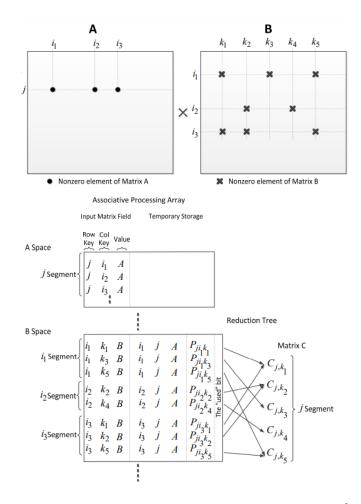

| 5.2  | Sparse matrix multiplication on associative processor from [248]. Matrices $A$ and $B$ , shown in the top half, are stored in the CAM. Each row stores a non zero value as a triplet of the row index, the column                                                                                                    |    |

|      | index and the value                                                                                                                                                                                                                                                                                                  | 89 |

8

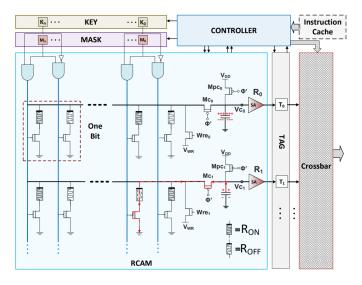

| 5.3  | Architecture of an associative processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

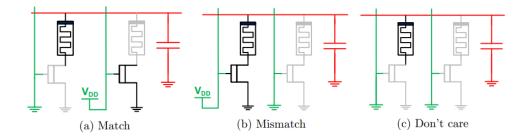

| 5.4  | Typical evaluation phases of a ReAP cell for the match (a), mismatch (b), and don't care (c) states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91        |

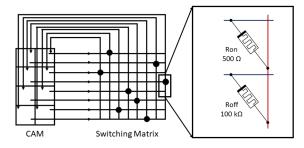

| 5.5  | Connection between the CAM and the SM. The black dots stands for<br>a short circuit which means that the input line connected to this dot<br>will be redirected to the output line connected to the CAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93        |

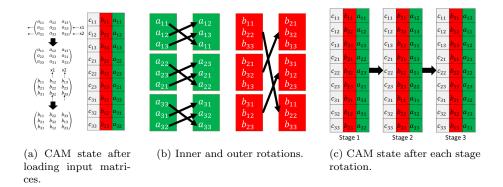

| 5.6  | The execution scheme of MM on ReAP with the loading phase in 5.6a<br>and the rotations after each stage in 5.6b. Intermediate CAM states<br>after rotations in 5.6c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94        |

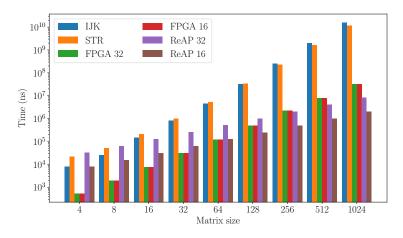

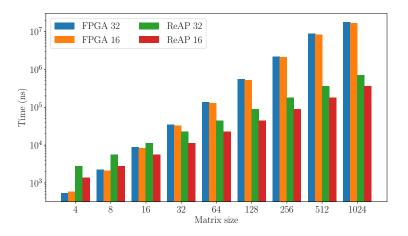

| 5.7  | Execution time in nsec for MM (left) and APSP (right) on an i7 CPU (IJK, Strassen), an FPGA and a ReAP for 16-bit and 32-bit data width.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96        |

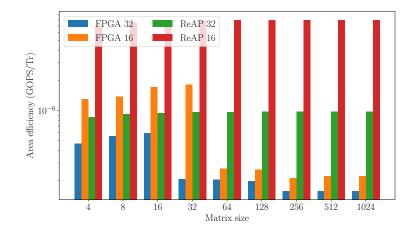

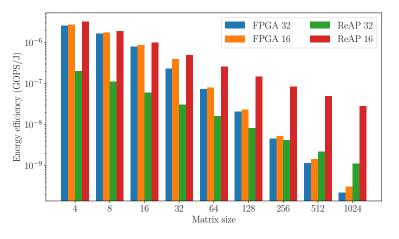

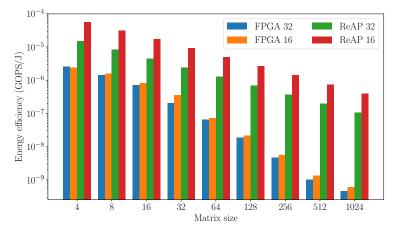

| 5.8  | Area efficiency in GOPS per transistor for MM (left) and APSP (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98        |

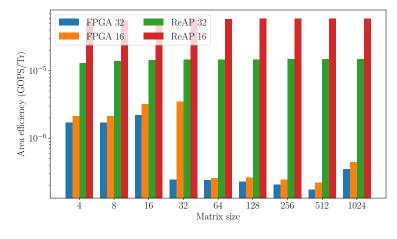

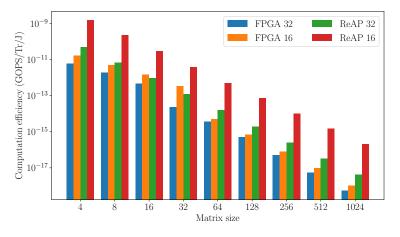

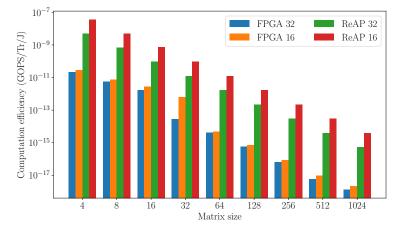

| 5.9  | Energy efficiency in GOPS per Joule for MM (left) and APSP (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99        |

| 5.10 | Computation efficiency in GOPS per transistor per Joule for MM (left) and APSP (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100       |

| 6.1  | Percentage of Multiply and ACCumulate (MACC), comparison (comp), addition (add), division (div) and exponent (exp) operations for different networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106       |

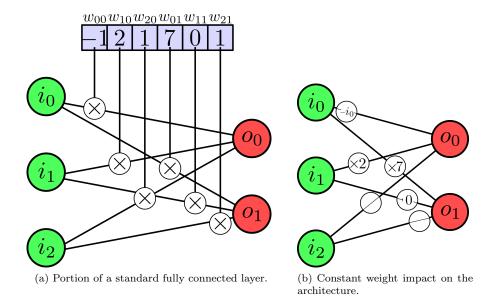

| 6.2  | Illustration of our idea with 6.2a, the network before constant-multiplication compression and 6.2b the result after customized multiplication compression.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | on<br>107 |

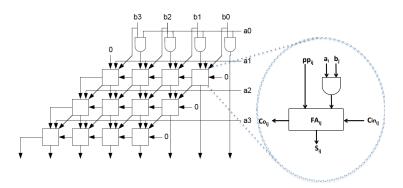

| 6.3  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 108       |

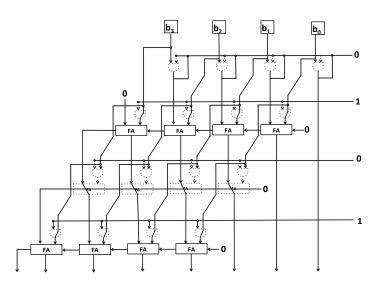

| 6.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110       |

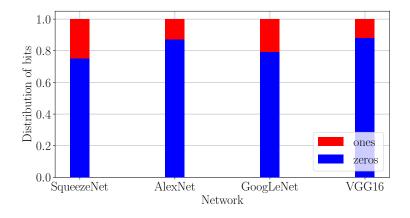

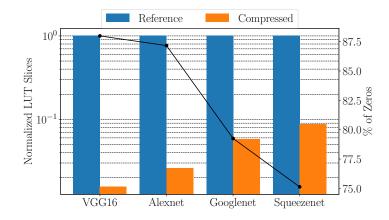

| 6.5  | Number of 'zero' bits compared to 'one' bits (normalized) in different<br>quantized Convolutional Neural Networks using a 7 bits fixed point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110       |

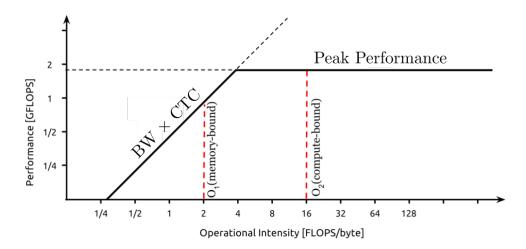

| 6.6  | Roofline model for two applications $O_1$ and $O_2$ . $O_1$ has less compute intensity and is memory bound since it has $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                               | 111       |

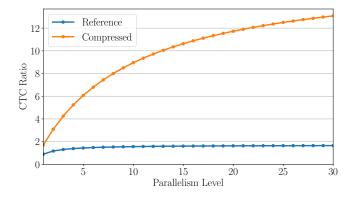

| 6.7  | Comparison of the parallelism level on the CTC ratio with and without our method.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113       |

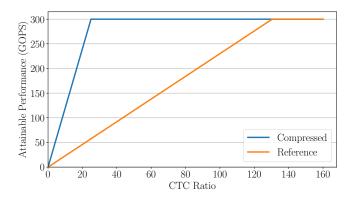

| 6.8  | The roofline model comparison with and without our method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113       |

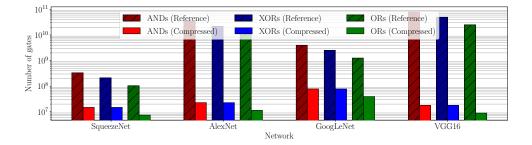

| 6.9  | Total number of logic gates required before and after applying our squeezing scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114       |

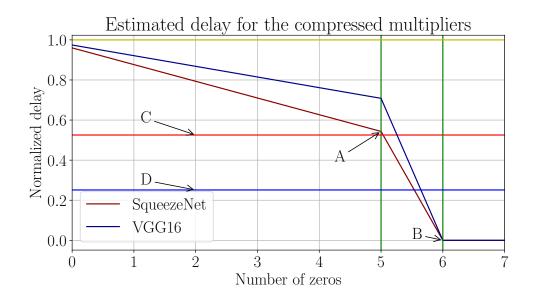

| 6.10 | The impact of the number of zero bits in network weights on the mul-<br>tiplier delay. The two series represent the delay when using our com-<br>pressed version (compressed) while varying the number of zeros in the<br>constant operand. The vertical green lines are the average number<br>of zeros from Figure 6.5 for the two networks. The intersubsection<br>gives the delay of the most common multiplier. This is point $A$ for<br>SqueezeNet and $B$ for VGG16. The lines $C$ and $D$ shows the averaged<br>delay over the parameters of SqueezeNet and VGG16 respectively                                                                        | 116       |

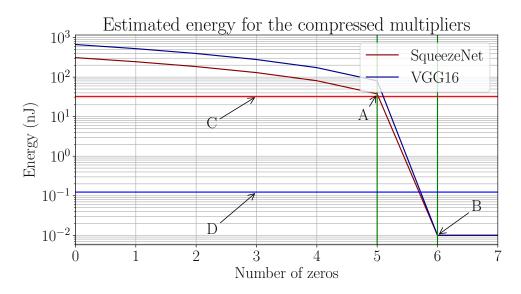

| 6.11 | The impact of the number of zeros in network parameters on the mul-<br>tiplier energy consumption compared to the conventional multiplier.<br>Similar to the delay, the two series present the decrease in energy<br>consumption for each zero in the constant operand. The $C$ and $D$<br>lines shows the average energy consumption over the parameters of<br>SqueezeNet and VGG16 respectively. $A$ and $B$ illustrate the energy<br>of the most common multiplier for these two networks respectively.<br>These values are obtained at the intersubsection between the average<br>number of zeros (green lines) and the delay of a compressed multiplier |           |

|      | with that number of zeros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 116       |

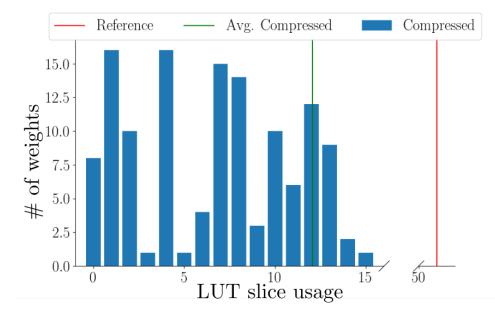

| 6.12              | Distribution of resource utilization for different compressed multipliers.<br>A comparison between the average of utilization over all possible128<br>multipliers (green line) and the utilization of the conventional imple-                                                                                                                       |            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.13              |                                                                                                                                                                                                                                                                                                                                                     | 118<br>119 |

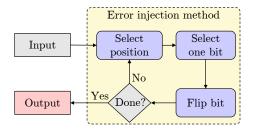

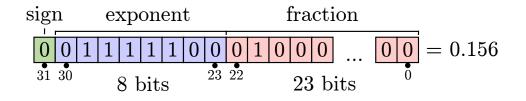

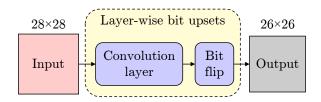

| 7.1<br>7.2<br>7.3 | Overview of the proposed method for soft error injection Description of the IEEE-745 single-precision floating-point format Our 2-layer model for simulating soft errors in activations is composed by a convolutional layer and our custom bit flip layer. The custom bit flip layer comprises a convolutional layer and a bit flip module applied | 124<br>125 |

| 7.4               | to the outputs of this convolutional layer                                                                                                                                                                                                                                                                                                          | 125<br>127 |

| 7.5               | Distribution of $\mathcal{A}_1$ over 1 million activations in logarithmic scale                                                                                                                                                                                                                                                                     | 128        |

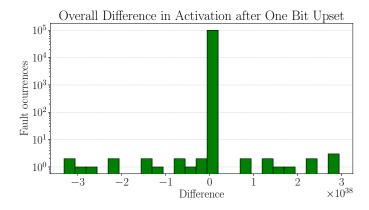

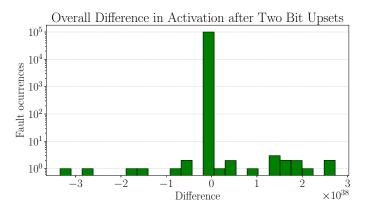

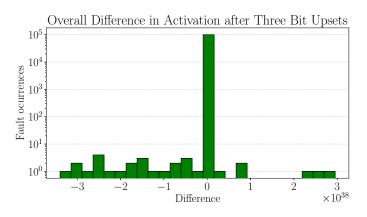

| $7.6 \\ 7.7$      | Distribution of $\mathcal{A}_2$ over 1 million activations in logarithmic scale<br>Distribution of $\mathcal{A}_3$ over 1 million activations in logarithmic scale                                                                                                                                                                                  | 128<br>128 |

| 7.8               | Comparison between single and multiple event transients and their                                                                                                                                                                                                                                                                                   | 120        |

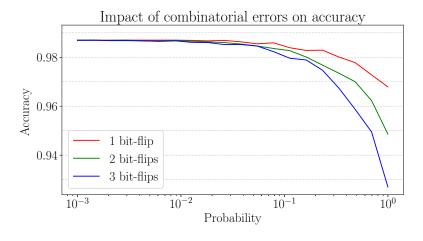

|                   | impact on overall LeNet-5 performance.                                                                                                                                                                                                                                                                                                              | 129        |

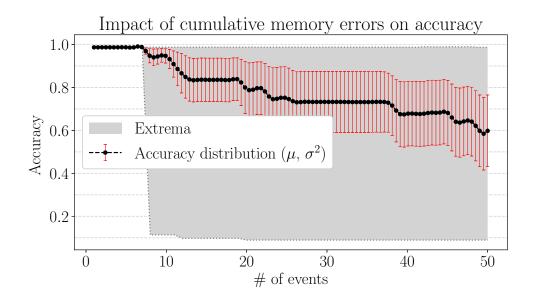

| 7.9               | Evolution of average accuracy (in black) when the number of errors augments. The dispersion and the extreme cases are shown in red and gray respectively.                                                                                                                                                                                           | 130        |

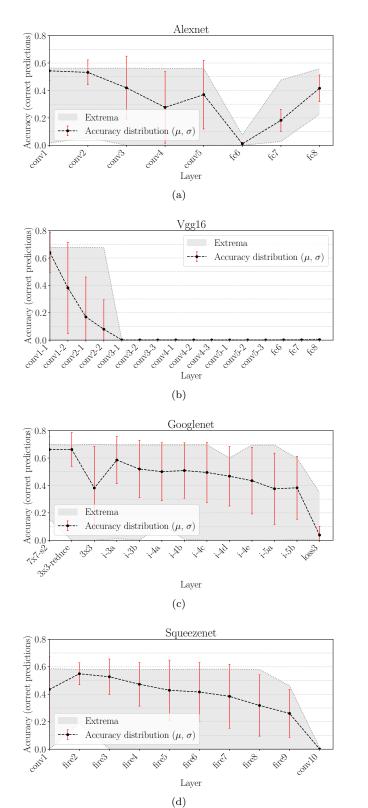

| 7.10              | Layer-wise analysis of memory soft-errors with independent responsi-<br>bility. Average accuracy is in black circles with the standard deviation<br>in red. The interval of extreme cases (minimum and maximum) is<br>illustrated with the gray region.                                                                                             | 131        |

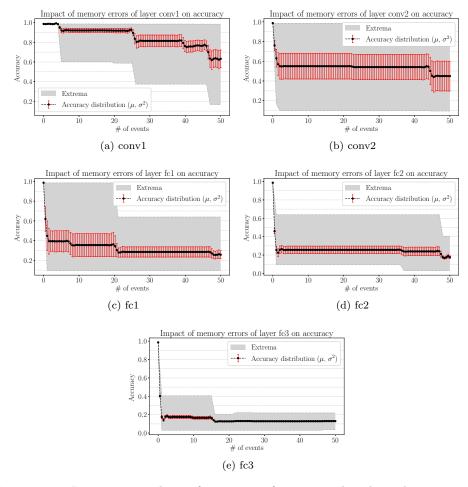

| 7.11              | Comparison between the 8-bit fixed point representation ( $Q$ ) of weights<br>and the 32-bit IEEE-754 representation ( $\mathcal{F}$ ). The results of different<br>runs are presented as the mean and the standard deviation of the top-1                                                                                                          | 131        |

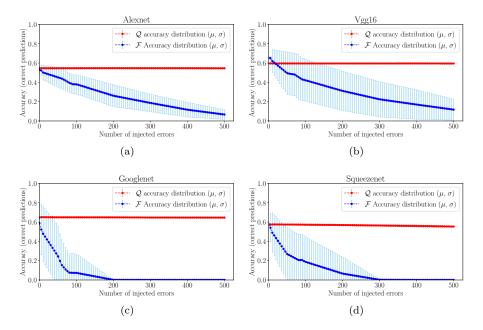

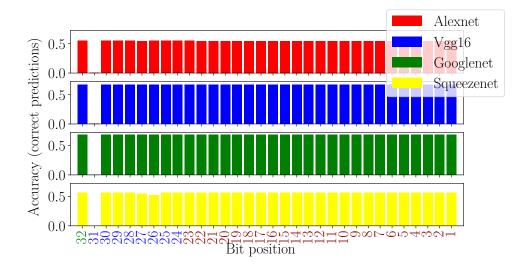

| 7 1 2             | accuracy                                                                                                                                                                                                                                                                                                                                            | 135        |

| 1.12              | accuracy. In the X-axis, red labels represent the mantissa, blue labels represent the exponent and the sign bit is in green.                                                                                                                                                                                                                        | 136        |

| 7.13              | Impact of faults layer-wise for the four networks. Each series is repre-<br>sented as the mean top-1 accuracy (black dots), the standard deviation                                                                                                                                                                                                  |            |

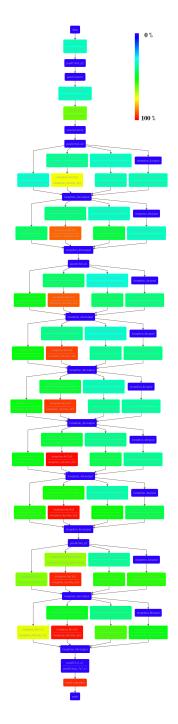

| 7.14              | (red error-bars) and the minimum/maximum (gray fill) Vulnerable layers in Googlenet represented with the same order of precedence used during execution. The background color of each layer                                                                                                                                                         | 137        |

|                   | represent its vulnerability.                                                                                                                                                                                                                                                                                                                        | 139        |

|                   |                                                                                                                                                                                                                                                                                                                                                     |            |

10

# List of Tables

| 2.1<br>2.2   | Example of a labeled dataset                                                                                                                                                                                                                                                              | 27<br>34                                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 3.1          | Summary of the key operating characteristics of each sensor as they apply to autonomous vehicles from [200]. AV stands for Autonomous Vehicles, CV for Connected Vehicles, CAV for Connected Autonomous Vehicles and DSRC for Dedicated Short-Range Communications                        | 40                                      |

| 3.2          | Driving datasets from [254]                                                                                                                                                                                                                                                               | 44                                      |

| 3.3          | Comparison of autonomous vehicle simulators. The environment ab-<br>breviations for urban and off-road columns are: T represent town, C<br>is for city, R is for road track and H for highway, F for forest, D for<br>desert, M for mountains, G for grassy field, U for underground mine |                                         |

|              | and H for harbor                                                                                                                                                                                                                                                                          | 46                                      |

| $4.1 \\ 4.2$ | CPU Classes from [92]<br>Comparison of State-of-the-Art Hardware Generators from [3]                                                                                                                                                                                                      | $\begin{array}{c} 63 \\ 77 \end{array}$ |

| 5.1<br>5.2   | LUT for Multiplication                                                                                                                                                                                                                                                                    | 91<br>92                                |

|              |                                                                                                                                                                                                                                                                                           |                                         |

| 6.1          | Energy savings relative to the reference implementation                                                                                                                                                                                                                                   | 119                                     |

| 7.1          | Number of weights (in millions) per network.                                                                                                                                                                                                                                              | 135                                     |

# Chapter 1

# Motivations and Thesis Objectives

## Contents

| 1.1 Deep Learning for Autonomous Vehicles 14 | 1 |

|----------------------------------------------|---|

| <b>1.2</b> Aim of Thesis                     | 5 |

| 1.2.1 Problem statement                      | 5 |

| 1.2.2 Constraints and Challenges             | 6 |

| 1.2.3 Thesis Objectives                      | 7 |

| 1.3 Main Contributions                       | 7 |

| 1.4 Outline                                  | 3 |

### 1.1 Deep Learning for Autonomous Vehicles

The recent years have known a constant increase in road users. This rapid growth has a direct impact on road accidents. The security and economic challenges that stem from this increase are of an immense magnitude. Human error, whether caused by fatigue, alcohol use or unsafe driving, is the major cause of traffic accidents. In a 2016 National Highway Traffic Safety Administration (NTHSA) report [205] in the USA, more than 94% of accidents are caused by human error.

According to the World Health Organization<sup>1</sup>, road traffic injuries are the **lead**ing cause of death for children and young adults aged 5-29 years. The number of death is estimated to 1.35 million per year. To put it into perspective, this number represents more deaths than those caused by alcohol use, drug use, fire, terrorism and natural disasters combined according to a statistic published by Amnesty International<sup>2</sup>. While human life concern is visibly the main impact, road traffic accidents cost most countries 3% of their gross domestic product. The annual social benefits of Autonomous Driving Systems are projected to reach \$800 billon by 2050 [255].

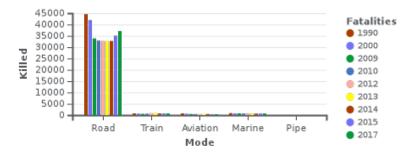

On a parallel comparison, fatalities caused by road accidents are the main challenge in transportation. Moreover, when comparing the death tolls in the field of transportation, we clearly see that most fatal accidents occur in road traffic. Figure 1.1 illustrates these tendencies as reported by the National Transportation Safety Board (NTSB) between the years 1990 and 2017<sup>3</sup>.

Figure 1.1: Comparison of fatalities caused by accidents in different transportation modes, data reported by the US' NTSB.

The European Commission released a new policy framework for road safety 2021-2030 [44] in May 2018 in order to deal with fatalities caused by road injuries. This new policy has a set of actions including the following:

- To make the vehicles we drive even safer.

- To make the infrastructure we drive on safer.

- To fund and finance investment in transport safety.

These policies have for goal to reduce fatalities by relying on safe autonomous systems. However, these systems have proven to be of high complexity. The unpredictability of road users' behaviour and the constant change of environment due to weather (sunny, rainy or snowy), time (day or night) and location (highway, city road or off-road) are major contributors to this complexity.

The recent advances in Artificial Intelligence (AI) ease the task of autonomous driving by providing highly capable algorithms that accurately assesses a situation. These algorithms rely on complex networks that are able to cope with the environment change and other users' behaviour. Successful deployment of these networks

<sup>&</sup>lt;sup>1</sup>https://www.who.int/news-room/fact-sheets/detail/road-traffic-injuries

<sup>&</sup>lt;sup>2</sup>https://ourworldindata.org/causes-of-death

<sup>&</sup>lt;sup>3</sup>https://www.ntsb.gov/investigations/data/Pages/Data\_Stats.aspx

have shown impressive reduction in fatalities per 100 million kilometers. The Tesla Autopilot for example have driven more than 3 billion kilometers with less than 10 reported fatalities. This accounts to 0.20 fatalities per 100 million kilometers. This number is estimated to be at 0.73 under traditional human control by the US Department of Transportation's 2016 fatal traffic crash data<sup>4</sup>.

The consistency of these numbers is only guaranteed with systems capable of running the most recent AI algorithms. However, the computing requirements are out of reach for today's platforms. In order to process a single  $400 \times 400$  image and locate driveable area as well as detect obstacles with only 53% accuracy, more then 140 GFlops<sup>5</sup> are needed. Running such algorithm constantly on all cameras deployed in the car and expecting an output at real time is beyond possibility. In addition, other sensors are needed when the environment changes. Cameras can not provide accurate perceptions in dark and obscure environments. The hardware platform needs to process all these inputs to carefully put the car in the right track. With more specialized hardware in the market, finding a single platform that can satisfies these performance constraints is challenging, especially with a limited budget in order to maintain a reasonable system overhead on the final price. Therefore, designing faster and efficient hardware is a key challenge for feasibility of ADS.

### 1.2 Aim of Thesis

Deep Learning has been established as a leading actor towards the developments of autonomous systems by revitalizing AI. For modern systems, it is inevitable to use these algorithms –or networks<sup>6</sup>– to cope with their increased complexity. While increasing the accuracy is a challenge, being able to deploy these networks should be a priority.

There are two phases when designing a deep neural network, namely, training and inference. The training phase is an offline process that generates a working instance of the network. The inference phase is when the network is ready to process inputs. During the deployment phase, we only need the training phase<sup>7</sup>. In this thesis, we focus on the deployment phase. At this stage, the network takes inputs from the environment using the various sensors deployed on the car and tries to predicts the best decision.

#### 1.2.1 Problem statement

Neural networks are compute hungry algorithms. The inference run on a single camera image requires more than 20 billion Multiply and Accumulate (MAC) operation. At peak performance, a 5 GHz Central Processing Unit (CPU) takes 4 seconds to process the image. By that time, the decision is obsolete and the situation is irrecoverable. In this thesis, we tackle this performance issue by proposing hardware architectures capable of handling this computation load.

This need in compute power is being fed by the increase in sensory demand. With higher levels of automation, the vehicle needs a complete environment perception. As seen in Figure 1.2, at least 28 sensory units are required for a mundane autonomous ride. These sensors continuously stream data to the compute units that need to be alerted at any given time to detect and react in case of danger.

Future autonomous vehicles will need an equivalent of a supercomputer rolling down the highway, generating and transmitting a overwhelming volume of data, up

<sup>&</sup>lt;sup>4</sup>https://www.nhtsa.gov/press-releases/usdot-releases-2016-fatal-traffic-crash-data

<sup>&</sup>lt;sup>5</sup>These numbers are obtained using a trained instance of Mask RCNN with 32-bit floating point weights and activations.

$<sup>^{6}</sup>$ Deep learning algorithms have similar structures as networks of artificial neurons. They are referred to as neural networks instead of the general appellation of algorithms, which is vaster.

<sup>&</sup>lt;sup>7</sup>Some networks are continuously trained, however we do not consider these algorithms in this study.

Figure 1.2: Sensor modules for each automation level from [251].

to 4 terabytes <sup>8</sup> per day per car. Deploying a massive hardware platform to handle these tasks would have dramatic impact on the cost, weight and energy consumption of the vehicle. For autonomous vehicles to be considered a safety replacement, efficient hardware need to be designed, aimed specifically at solving these challenges.

An other issue that is under-explored by researchers in machine learning is reliability. In this thesis we will also tackle the problem of whether these algorithms should be trusted for safety-critical systems such as autonomous driving. ADS should adhere to strict safety standards such as ISO 26262:2018 [100] and ISO/PAS 21448:2019 [101] specially addressing the safety of Advanced Driver Assistance Systems (ADAS) functions in road vehicles. The reliance on machine learning puts ADSs in a gray area when it comes to these standards due to their lack of traceability and unpredictability [120].

#### **1.2.2** Constraints and Challenges

As far as inference is concerned, many platforms exist to satisfy these constraints. However, for a commercial system, efficiency is always the next challenge after feasibility. Designing efficient hardware for self-driven cars is crucial to their functioning. Many major companies addressed this problem for their autonomous vehicle projects. For instance, Tesla's Hardware 2 uses the NVIDIA DRIVE PX 2 AI computing platform. The platform costs around 15,000  $\notin$  per unit. This price is compared to that of the most sold car in 2019, the Toyota Corolla. On the other hand, Google have designed a novel architecture, the Tensor Processing Unit (TPU), that is dedicated to machine learning algorithms. The TPU is deployed on the cloud and could be rented for research. In the academic community, Field Programmable Gate Array (FPGA) accelerators are widespread. However, these accelerators trade the accuracy of the system for performance. This trade-off is not possible for a safety-critical system such as autonomous vehicles.

As for reliability, this problem seems to be ignored. Researchers focus on improving the accuracy of the network. This accuracy is then traded for performance with no concern on reliability. This is partly since machine learning algorithms are not yet considered for safety-critical systems and are always supervised by a human expert.

<sup>&</sup>lt;sup>8</sup>https://datacenterfrontier.com/rolling-zettabytes-quantifying-the-data-impact-of-connected-cars/

This trend is changing. The accelerator for machine learning needs to be resilient to faults if deployed in aggressive environments.

#### 1.2.3 Thesis Objectives

In this thesis, we tackle the problem of performance and reliability for machine learning accelerators deployed in autonomous vehicles. In the performance study, the usual tradeoff between accuracy and performance is not tolerated. As for the reliability study, we aim to locate the vulnerable components of the software, i.e. the network, and the hardware.

### **1.3** Main Contributions

The thesis focus on designing hardware for autonomous vehicles. The problem was tailored down to designing machine learning accelerators. In this thesis, we propose two architectures of hardware accelerators for machine learning.

The first architecture can be seen in Chapter 5. In this chapter, we used a memristor-based implementation of an associative processor, the Resistive Associative Processor (ReAP), to solve the performance problem of machine learning for autonomous systems like self-driving cars. The motivations behind this choice are the von Neumann bottleneck and it's implications on the performance of the system. In our ReAP, all computations are done inside the memory which solves this problem. The accelerator compares very well to a Xilinx reference design with less than 2 ms for a 1024  $\times$  1024 matrix multiplication, two orders of magnitude less than the Xilinx design. In terms of general compute efficiency, measured as GOPs per Watt per transistor, comparisons shows a staggering difference with a major gap between our design and the Xilinx design. This was mainly due to the efficient usage of resources for storage and compute at the same time. The results of this work has been published in [163],

Our second contribution is on FPGA and is detailed in Chapter 6. We exploit the fact that weights are constant after training. Therefore, we designed an accelerators dedicated to a trained instance of a network. In any given design, the multipliers require a weight and an input. Since weights are constant, we design dedicated multipliers that only takes one operand, the input. This results in a inflexible design since these multipliers can no longer be reused. However, this flexibility is traded for performance and resource utilization which is a novel contribution compared to other state of the art accelerators where the main tradeoff happens between accuracy and performance. Moreover, since weights are embedded in multipliers, no storage is needed. Simplifying storage have huge implication on the architecture since no time is needed to load weights from the input and the memory would be free to store more inputs. Results of this work has been partially published in [153].

As stated earlier, the second axis of this thesis is reliability. While machine learning has been extensively studied in the past few years from an acceleration and quality point of view, research about how reliable these network are against faults and attacks are meagre. The results of this work shows that reliability is an important issue for safety of machine learning-based systems. The accuracy with which the system has been deployed can be substantially compromised. This was a two step contribution given in details in Chapter 7. First, we propose a study to test if there is a problem when the hardware accelerator is exposed to errors. In this first part, we discovered that the combinatorial part of the circuit is resilient however, memory errors can prove to be dramatic. This first contribution was published in [165]. In the second study, we focus on the nature of errors. We compare the different representations and how they compare to each other. The results of this work is published in [161]. In parallel, a tool was made publicly available<sup>9</sup> to test the resilience

<sup>&</sup>lt;sup>9</sup>https://github.com/cypox/CNN-Fault-Injector

of a CNN and to isolate the vulnerable layers that needs.

From a system point of view, we designed a streaming platform that uses CPUs and FPGAs to conduct data from a sensory unit, for instance, a camera, to the accelerator. The design undergoes a study on the input to choose the optimal size that allows components to communicate efficiently with minimal loss in accuracy and performance. The results of this work were published in [162]. An other study on sensor fusion was conducted to show a way of merging the camera and the LiDAR inputs, two totally different representations cooperating to perform road extraction and obstacle detection. This work was partially published in [168]. We also propose a high level framework in [81] that incorporate the cloud and the fog in the detection process. Communication with these components is key to achieving full safe driving.

#### 1.4 Outline

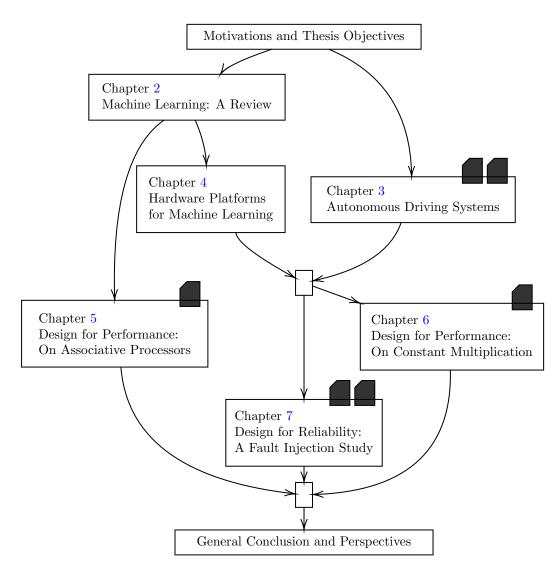

This thesis is structured as follows. First we give our reasons on why we considered machine learning algorithms as a solution for the driving problem. This is presented int Chapter 2 along with the required knowledge on field to understand later chapters. We conclude the chapter with a review on recent algorithms, their architectures and performances. An in-depth study on ADS is given in Chapter 3. We present the challenges of autonomy in self-driving cars from a hardware point of view. In Chapter 4 we give our state-of-the-art study on hardware accelerators for machine learning that may apply to the autonomous driving scenario. Two novel accelerator designs were presented in Chapters 5 and Chapter 6. Our reliability study is shown in Chapter 7. We conclude the thesis with a summary and some research perspectives in Chapter 8. The dependencies between chapters are shown in the flow graph in Figures 1.3.

Figure 1.3: The reading dependencies between chapters. Chapters with the black document icon in the top right corner contain details of at least one peer-reviewed publication.

# Chapter 2

# Machine Learning: A Review

#### Contents

| 2.1 | Arti  | ficial Intelligence and Machine Learning | <b>24</b> |

|-----|-------|------------------------------------------|-----------|

| 2.2 | Mot   | ivations Behind Machine Learning         | <b>25</b> |

| 2.3 | How   | it works?                                | 26        |

|     | 2.3.1 | The back propagation algorithm           | 26        |

|     | 2.3.2 | ANN Architecture                         | 28        |

|     | 2.3.3 | CNN Architecture                         | 30        |

|     | 2.3.4 | The Convolutional Layer                  | 30        |

| 2.4 | Data  | sets                                     | 31        |

| 2.5 | Com   | mon CNN Architectures                    | 31        |

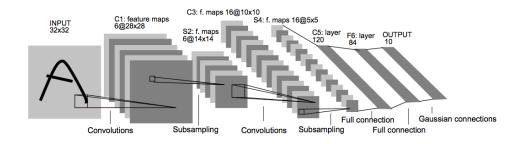

|     | 2.5.1 | LeNet-5                                  | 31        |

|     | 2.5.2 | AlexNet                                  | 32        |

|     | 2.5.3 | VGG16                                    | 33        |

|     | 2.5.4 | GoogleNet                                | 33        |

|     | 2.5.5 | SqueezeNet                               | 33        |

| 2.6 | CNN   | Profiling                                | 33        |

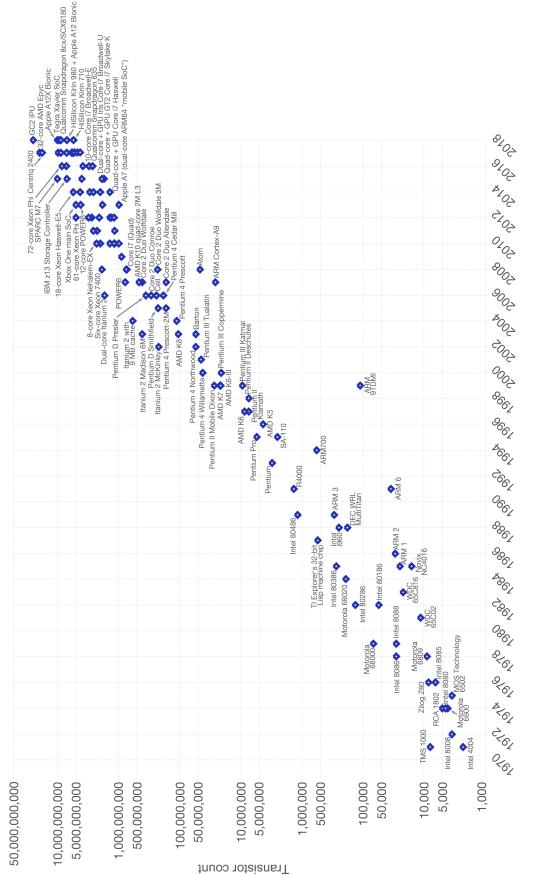

While Moore's law is in decline for single-core processors, parallel computing is correcting the slope for the past decade in order to maintain the performance increase each year as can be seen in Figure 2.1. With this law being true for half a century, processing power became abundant. Today's computers are able to perform incredible feats.

Computer vision is one of the fields that harnessed this power. Ideas that requires large data operations became possible. Limited by the available compute power back then, these algorithms remain dormant for a long time. The, arguably biggest, milestone achieved recently was witnessed in ILSVRC 2015 when AlexNet, a CNN, raised the bar by beating other algorithms and even human accuracy at guessing the class of an image from 1000 possible classes.

In this chapter we walk through these algorithms. We first explain the motivations that lies behind the choice of machine learning over other approaches. We also give an insight on how most famous machine learning algorithms operates. Later on, we present a profiling study to analyze the characteristics and requirements of these algorithms.

### 2.1 Artificial Intelligence and Machine Learning

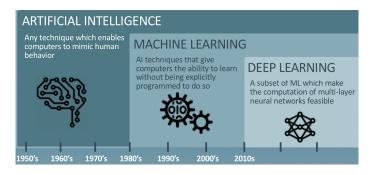

Machine learning is a sub-category of AI. AI encompass any algorithm that enables computers to mimic human behavior as can be seen in Figure 2.2. Examples of these algorithms are rule-based or expert systems usually used for medical diagnosis where all the outputs of a problem (in this cases diseases) are listed with all the possible inputs (symptoms in the case of medical diagnosis). While this basic is useful in some fields, it does not scale with the problem size where the human expert needs to pass a large amount of information to the computer. The ability to learn without being explicitly programmed was the follow-up of AI algorithms and is what we refer to as machine learning.

Figure 2.2: Timeline of the advances in artificial intelligence and the rise of machine learning.

In ML, the explicit programming was replaced with a learning phase. In this phase the machine is *taught* how to solve a problem. Once done, the second phase follow and is called the inference phase. In this phase, the algorithm is deployed and is ready to perform the task it was trained for.

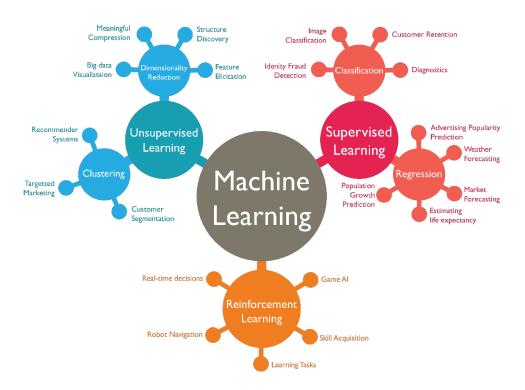

Depending on the training phase, many types of ML algorithms arises. In [16], six types were discussed:

- Supervised learning: this is the most common form of ML algorithms. In this class, a labeled dataset is used to train the algorithm. During this training, the algorithm will extract the similar characteristics of elements with the same label to classify a given input into the most adequate class. A common misconception is that supervised learning is classification. This is false since regression -where the algorithms learns the evolution of an output based on input variations- and detection -where the algorithm learns how to distinguish and separate objects-are also algorithms with a supervised training.

- Unsupervised learning: the difference between the supervised and the unsupervised learning is the dataset. In this class, no labels are given. During the learning phase, the algorithm learns the existing similarities between samples in the dataset as stated in [69].

- Semi-supervised learning: this type of ML algorithms is somewhere between the first two. The dataset contains some labeled samples but may contains items with no labels. The training algorithm should be able to process both samples in order to learn features from the dataset.

- Reinforcement learning: in this class of algorithms, no dataset is present. Learning consist on finding the best policy that an agent should follow in a simulated environment in order to achieve a goal. When interacting with said environment, the agent receives reward for positive decisions and penalties for negative ones. This reward mechanism helps the agent find the best policy.

- Transduction: this is not a very common class in ML. Similar to supervised learning, the algorithm tries to map an input to an output based on a given dataset. The main difference being, transduction algorithms does not explicitly construct a mapping function but predicts outputs based on the dataset.

- Learning to learn: this is a new class of ML algorithms. It falls under the category of **self-aware** systems. In this class, the algorithms learns its own inductive bias based on previous experience.

Figure 2.3: Classification of ML algorithms and sub-categories of each class with some example algorithms are given at the nodes of each sub-category.

In Figure 2.3 we show the most common types of ML algorithms, namely, supervised, unsupervised and reinforcement learning. In these algorithms, the quality of the algorithm highly depends on the quality of samples in the dataset. The exception being for reinforcement learning where no dataset is present. In this case, the quality depends on how well the environment is simulated and the reward-penalty system is designed.

### 2.2 Motivations Behind Machine Learning

As stated in [167], the two biggest drivers of the recent progress of machine learning are **computational scale** and **data availability**. The first cause was discussed in the introduction of this chapter with the introduction of parallel processing in the recent compute platforms. As for the second, data abundance is clearly visible with the widespread of social media applications.