## Thèse de doctorat

Pour obtenir le grade de

## Docteur de l'Université Polytechnique Hauts de France

### Discipline: Informatique

Présentée et soutenue par: Alexandre CHABOT.

Le 03/02/2020, à Gif-sur-Yvette

#### Ecole doctorale :

Sciences Pour l'Ingénieur (SPI)

Equipe de recherche, Laboratoire :

Laboratoire d'Automatique, de Mécanique et d'Informatique Industrielles et Humaines (LAMIH) Laboratoire Sûreté des Logiciels (CEA/LIST/DILS/LSL)

## Reliability-Guided Design Space Exploration for Safety-Critical Applications - Exploration des Architectures des Systèmes Embarqués Dirigée par la Fiabilité

#### Président de jury et Rapporteur:

• Alberto Bosio. Professor, Ecole Centrale de Lyon

#### Rapporteur

• Francois Pecheux. Professor, Sorbonne Université -LIP6

#### Examinateurs

• Karine Heydemman. Professor, Sorbonne Université -LIP6

- Ansgar Radermacher. Research Engineer, CEA LIST

- Youri Helen. Research Engineer, CEA LIST

#### Directeurs de thèse

• Smail NIAR. Professeur, UPHF

#### Co-encadrant de thèse

- Ihsen Alouani. Maitre de Conférences, UPHF

- Réda Nouacer. Ingénieur de Recherches, CEA

## **Declaration of Authorship**

I, Alexandre CHABOT, declare that this thesis titled, "Reliability-Guided Design Space Exploration for Safety-Critical Applications" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Date: 03 February 2020

"Everybody is a genius. But if you judge a fish by its ability to climb a tree, it will live its whole life believing that it is stupid"

Albert Einstein

## UNIVERSITÉ POLYTECHNIQUE DES HAUTS DE FRANCE

## Abstract

Faculty Name Department or School Name

Doctor in Computer Sciences

Reliability-Guided Design Space Exploration for Safety-Critical Applications

by Alexandre CHABOT

Technological advances allow the production of increasingly complex electronic systems. Nevertheless, technology and voltage scaling increased dramatically the susceptibility of new devices not only to Single Bit Upsets (SBU), but also to Multiple Bit Upsets (MBU). In safety critical applications, it is mandatory to provide fault-tolerant systems, providing high reliability while responding to applications requirements. The problem of reliability is particularly expressed within the memory which represents more than 80% of systems on chips.

To tackle this problem we propose a new memory reliability enhancement techniques called DPSR: Double Parity Single Redundancy, designed to answer SBU and MBU problematic. To evaluate our proposition we modify historically used simulation single fault injection model by adding memory monitoring and MBU injection and compare it to state of the art fault injection engines. Based on a thorough fault injection experiments, DPSR shows promising results. It detects and corrects more than 99.6% of encountered MBU and has a performance overhead of less than 3% in mean. Our fault injection methodology shows also promising results by discovering more than 11% of incorrect behavior after fault injection than the classical single bit random injection.

Keywords: Reliability, DPSR, SBU/MBU, Fault Injection, Memory

#### French Abstract:

Les avancées technologiques ont permis la production de systèmes électroniques de plus en plus complexes. A l'ombre de ces évolutions, la diminution de la taille des transistors ainsi que la diminution de tension ont dramatiquement impactés la sensibilité aux fautes de ces nouvelles plateformes électroniques. Leur susceptibilité aux fautes multiples a également été tout d'abord découverte puis augmentée. Dans les applications critiques, il est obligatoire de fournir des systèmes résistants aux fautes tout en conservant un comportement identique à celui attendu peu importe les conditions. Le problème de fiabilité est tout particulièrement exprimé dans la mémoire car elle représente aujourd'hui plus de 80% de la totalité de la surface des plateformes électroniques.

Pour adresser ce problème de fiabilité, nous avons proposé dans nos trois

ans de recherche une nouvelle technique améliorant la fiabilité appellée DPSR (Double Parity Single Redundancy traduit littéralement par Double Parité associée à une Simple Redondance). Cette technique est désignée tout particulièrement pour contrer les soucis de fautes simples et multiples. Pour évaluer notre technique, nous avons modifié les modèles permettant de faire des injections simples en y ajoutant des paramètres supplémentaires comme la surveillance de l'utilisation mémoire. Ce modèle a également été enrichi de la possibilité d'injecter des fautes multiples. Nous avons au cours de ces années de recherche comparé notre modèle aux modèles existants. Basé sur de longues expérimentations, notre technique DPSR a montré des résultats prometteurs avec plus de 99.6% de fautes mutiples corrigées et détectées en introduisant une perte de seulement 3% de performance. Notre modèle d'injection a également montré des résultats prometteurs en découvrant plus de 11% de comportements non désirés que si on utilisait une méthode d'injection de l'état de l'art.

Mots Clés: Fiabilité, DPSR, Fautes Multiples, Injection de Fautes, Mémoire

## Acknowledgements

La thèse étant un marathon plus qu'un sprint, il est indispensable de s'entourer des bonnes personnes et il est impossible de mener une thèse à bien sans un entourage personnel et professionnel de qualité. Cette partie de remerciements me permet notamment de remercier chaque personne qui a participé de près ou de loin, directement ou indirectement à ce que je présente aujourd'hui. Je voudrais commencer par remercier les membres du jury qui ont pris de leur temps ...

Dans un second temps je voudrais remercier tout particulièrement mes encadrants de thèse. Smail Niar qui a été un guide avec ces précieux conseils. Il a su gérer mes errements administratifs et s'est toujours montré bienveillant vis à vis de moi. Ses remarques et son implication ont été précieux tout au long de cette thèse. Réda Nouacer qui avec sa bonne humeur et nos conversations autour de mon sujet mais aussi autour de la vie de chercheur et des conseils de vie qu'il a su me donner m'ont fait grandir tout au long de la thèse. Enfin, Ihsen Alouani a su venir me challenger scientifiquement avec ses questions, ses remarques et sa sympathie a su faire grandir et murir des idées que j'avais pour donner des articles. Il sortait tout juste de son doctorat quand on s'est rencontré et aujourd'hui il est maître de conférence, une reconnaissance méritée au vu de la qualité de son travail et de sa connaissance en différents domaines.

Même si je ne suis pas venu souvent à Valenciennes, j'ai établi des connexions avec différents doctorants du lamih. Un gros merci à Hannen, Ayoub et Ismat pour leur gentillesse, leurs sourires et leurs bon conseils. Un merci à tout les autres avec qui je n'ai pas eu la chance de partager autant mais qui m'ont toujours bien accueilli.

Basé à Nano-Innov j'ai évidement lié des liens tout particuliers avec tout les membres du laboratoire LSL. Merci à eux pour leur accessibilité et leur bienveillance. Je pense notamment à Florent Kirschner qui a toujours été franc et ravi de voir mes avancés pendant ma thèse. Un merci à Gilles et Yves qui ont toujour été disponibles pour répondre à mes différentes questions techniques et qui m'ont toujours accordé du temps quand j'en avais besoin. Merci à Zaynah qui était un peu ma tata pendant la thèse, elle, qui sait la difficulté que c'est de grandir en tant que chercheur et qui a toujours su venir partager des moments bons comme mauvais avec moi. Un merci évidement à Frédérique qui est particulierement compétente et qui est un organe essentiel du laboratoire. Merci également à Julien qui s'est montré à l'écoute de mes questions notamment académiques. Merci à Zakaria et David pour nos discussions et leur bonté tout au long de mes trois années. Hors du laboratoire j'ai pu notamment noué des liens avec Quentin, Agnès, Onder qui malgré les distances entre nos bureaux ont toujours montré de la curiosité pour mon travail

Je souhaite également remercier à part les non permanants du laboratoire qu'ils soient stagiaires, doctorants ou post doctorants. Je pense à mes cobureaux comme Quentin et Quentin B., Guillaume, Marc, Dongho, Thibault et Virgile avec qui la cohabitation a toujours été agréable et qui m'ont permis de décompresser parfois. Une grosse pensée pour Florent qui est toujours prêt à discuter de n'importe quel sujet avec cette pointe d'humour qui fait de la discussion un plaisir. Merci à Christophe qui est une force tranquille et dont la bonne humeur reste inchangée peu importe l'heure de la journée. Merci à Zinab et ne t'en fais pas tout ira bien pour toi j'en suis sûr. Evidement merci à Hugo, mon ami qui est dorénavant bien plus qu'un simple collègue de boulot pour nos discussions intellectuels autour du ballon rond mais aussi et surtout autour de tout et de rien.

Enfin, je ne serais pas là sans le soutien indéfectible de toute ma famille. Que ce soit mes grands-mères ou mon grand-père, ils ont toujours su s'investir dans mon projet et me soutenir. Merci à mes tontons et tatas pour tout. Merci à Gaêlle pour ta gentillesse, tes bons conseils et nos franches rigolades. Merci à Tom pour ta candeur due à ton âge et ton sourire à chaque fois qu'on se voit. Un énorme merci à Maman et Papa, vous êtes merveilleux et vous avez fait de ces trois ans un long fleuve tranquille. Vous étiez là pour les bons comme les mauvais moments, toujours derrière moi avec cette confiance et cet amour que vous me portez sans relâche. Finalement, je vais remercier Laura, ma compagne avec qui j'ai vécu pendant toute cette thèe et qui partage ma vie depuis 8 ans maintenant. Tu as accepté mes départs, mes voyages, mes horaires, mes travaux hors des horaires de bureaux et surtout tu m'as soutenu tout au long des trois ans. Je ne pouvais pas rêver mieux.

xiii

# Contents

| D  | eclara | ntion of | Authorship                                              | iii  |

|----|--------|----------|---------------------------------------------------------|------|

| Al | ostrac | zt       |                                                         | viii |

| A  | cknov  | wledge   | ments                                                   | xi   |

| 1  | Intr   | oductio  | on                                                      | 1    |

| 2  | Stat   | e of the | e Art                                                   | 5    |

|    | 2.1    | Fault '  | Турез                                                   | 6    |

|    |        | 2.1.1    | Multiple Bit Upsets                                     | 8    |

|    |        | 2.1.2    | Probabilistic Model                                     | 10   |

|    |        | 2.1.3    | Fault Consequences                                      | 12   |

|    | 2.2    | Fault    | Injection Techniques                                    | 14   |

|    |        | 2.2.1    | Fault Injection Overview                                | 15   |

|    |        | 2.2.2    | Simulation-Based Fault Injection                        | 17   |

|    | 2.3    | Reliab   | vility Techniques and Means                             | 19   |

|    |        | 2.3.1    | Global View of Reliability Enchancement Techniques .    | 20   |

|    |        | 2.3.2    | Global Memory Reliability Techniques                    | 22   |

| 3  | Dou    | ible Pa  | rity bit Single Redundancy                              | 29   |

|    | 3.1    | Preser   | ntation and Motivation                                  | 30   |

|    | 3.2    | Proba    | bilistic comparison between existing memory reliability |      |

|    |        | techni   | ques and DPSR                                           | 32   |

|    |        | 3.2.1    | Detection                                               | 33   |

|    |        | 3.2.2    | Correction                                              | 34   |

|   |             | 3.2.3   | Memory Space                                          | 35 |

|---|-------------|---------|-------------------------------------------------------|----|

|   |             | 3.2.4   | Discussion                                            | 36 |

|   | 3.3         | RETG    | Reliability Enhancement Technique Grade               | 36 |

| 4 | Stru        | cture o | of the Fault Injector                                 | 39 |

|   | 4.1         | Overv   | 7 <b>iew</b>                                          | 40 |

|   | 4.2         | Memo    | bry Accesses Impact onto Fault Injection              | 41 |

|   | 4.3         | Multij  | ple Bit Upsets in the Model                           | 42 |

|   | 4.4         | Globa   | l Algorithm                                           | 43 |

|   | 4.5         | Other   | Injection Modes                                       | 46 |

|   |             | 4.5.1   | Random Injection                                      | 46 |

|   |             | 4.5.2   | Determined Injection                                  | 47 |

| 5 | Exp         | erimen  | tal Results                                           | 49 |

|   | 5.1         | Exper   | imental Setup                                         | 50 |

|   | 5.2         | Evalu   | ation of our Injection Tool                           | 53 |

|   |             |         | Efficiency                                            | 54 |

|   |             |         | Representativeness                                    | 57 |

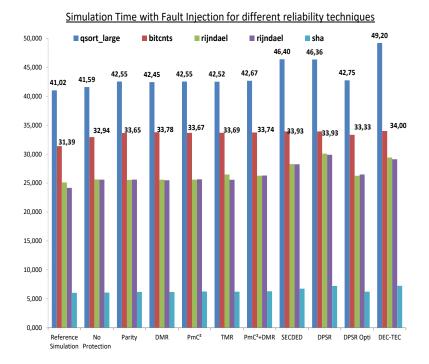

|   |             | 5.2.1   | Simulation Overhead                                   | 59 |

|   | 5.3         | RETG    | computation                                           | 62 |

|   |             | 5.3.1   | Memory Reliability Techniques impact onto performance | 62 |

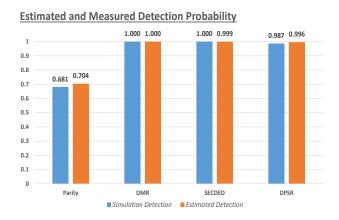

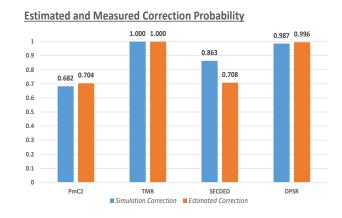

|   |             | 5.3.2   | Mathematical Approach Verification                    | 64 |

|   |             |         | Detection Probability                                 | 65 |

|   |             |         | Correction Probability                                | 65 |

|   |             | 5.3.3   | Memory Reliability Techniques Comparison              | 66 |

|   |             | 5.3.4   | RETG estimation                                       | 67 |

| 6 | Con         | clusior | 1                                                     | 69 |

| A | App         | endix . | Α                                                     | 73 |

|   | A.1         | List of | f Usefull Parameters to Configure Fault Injection     | 73 |

|   | A.2         | Explic  | cations                                               | 77 |

| B | App         | endix ] | В                                                     | 79 |

|   | <b>B</b> .1 | Exam    | ple of a Script Used During Test Campaign             | 79 |

|   | B.2         | Explic  | cations                                               | 83 |

| C Publications | 85 |

|----------------|----|

| Bibliography   | 87 |

# List of Figures

| 2.1 | Failure Rate Evolution During Life Periods For An Electrical    |    |

|-----|-----------------------------------------------------------------|----|

|     | System [21]                                                     | 8  |

| 2.2 | Single and Multi Bit Upset (BU) percentages by technology       |    |

|     | nodes in nm for SRAMs [19]                                      | 9  |

| 2.3 | Representation of Fault Injection Environment                   | 15 |

| 2.4 | Representation of a System                                      | 19 |

| 2.5 | Parity Functioning                                              | 23 |

| 2.6 | TMR Functioning                                                 | 23 |

| 2.7 | PmC2 Functioning                                                | 24 |

| 2.8 | SECDED example for 8 bits data word                             | 25 |

| 3.1 | DPSR Write for 8 bits word                                      | 32 |

| 3.2 | DPSR Read for 8 bits word                                       | 32 |

| 4.1 | The Fault Injection Model                                       | 40 |

| 4.2 | Example of a set of parameters (extracted from FIDES standard)  | 43 |

| 4.3 | Fault Injection Strategy                                        | 47 |

| 5.1 | Representation of UNISIM-VP environment for ARMv7 simu-         |    |

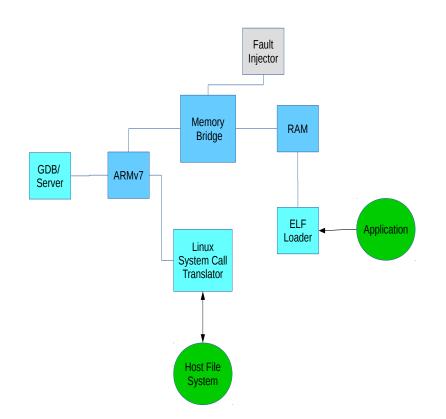

|     | lations.                                                        | 52 |

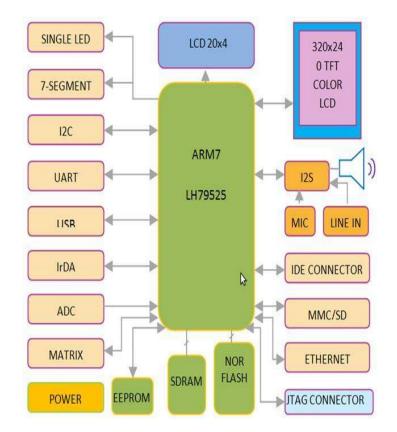

| 5.2 | Representation of ARM7 architecture [39] which use a ARMv7      |    |

|     | simulator                                                       | 53 |

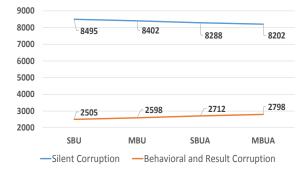

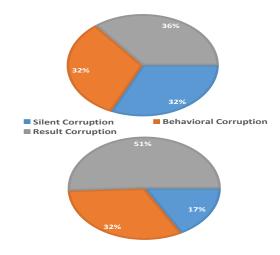

| 5.3 | Type of observed corruption with different injection procedures |    |

|     | on Susan smooth bench with 11000 runs for each procedure        | 54 |

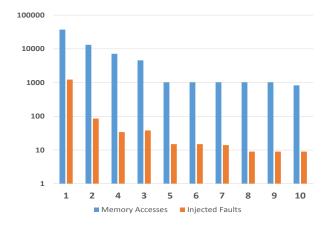

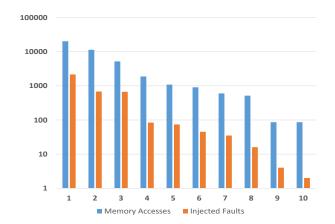

| 5.4  | Memory access locality compared to Injection locality for Su-     |    |

|------|-------------------------------------------------------------------|----|

|      | san Corner Mode Application. Values are given for the 10 (x-      |    |

|      | axis) most accessed memory zones                                  | 56 |

| 5.5  | Memory access locality compared to Injection locality for Su-     |    |

|      | san Smooth Mode Application. Values are given for the 10          |    |

|      | (x-axis) most accessed memory zones.                              | 56 |

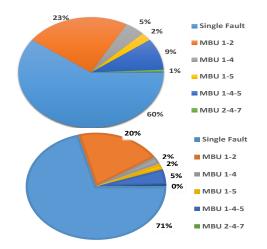

| 5.6  | Repartition of injected upsets patterns given by Table 4.2 (top)  |    |

|      | and those injected by our model (bottom)                          | 57 |

| 5.7  | Single (top) and 2-BU (bottom) corruptions distribution           | 58 |

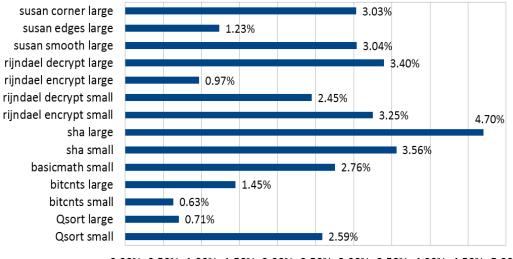

| 5.8  | Simulation time increase after implementing fault injection mod-  |    |

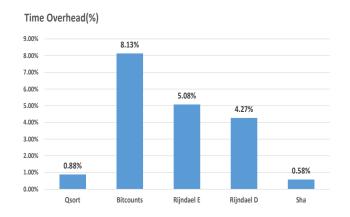

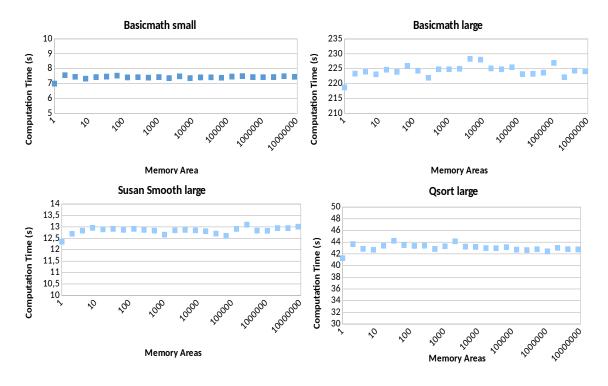

|      | ule                                                               | 60 |

| 5.9  | Simulation Overhead due to read and write monitoring with-        |    |

|      | out memory protection                                             | 61 |

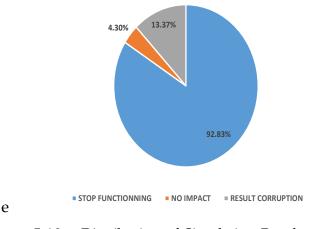

| 5.10 | Distribution of Simulation Results after Read Fault Injection     |    |

|      | on unprotected system for different application on 19000 runs     | 62 |

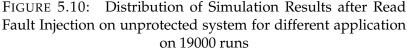

| 5.11 | Computation Time modification due to memory areas number          | 63 |

| 5.12 | Simulation Time (seconds) with fault injection for different re-  |    |

|      | liability techniques                                              | 64 |

| 5.13 | Estimated and Observed Detection Probability of different re-     |    |

|      | liability techniques during simulation with a realistic fault in- |    |

|      | jection                                                           | 65 |

| 5.14 | Estimated and Observed Correction Probability of different re-    |    |

|      | liability techniques during simulation with a realistic fault in- |    |

|      | jection                                                           | 66 |

# List of Tables

| 2.1 | Cumulative 2-Bit Event Count Normalized to 1000 for 150nm      |    |

|-----|----------------------------------------------------------------|----|

|     | SRAMs for Different Particle Strikes Energy (MeV) [49]         | 10 |

| 2.2 | Pattern Injection Square                                       | 10 |

| 2.3 | Code Example 1                                                 | 14 |

| 2.4 | Fault Injection Methodologies comparison                       | 17 |

| 2.5 | Comparison of Fault Injection Tools                            | 19 |

| 3.1 | Detection probability of memory reliability techniques for 22  |    |

|     | MeV particle strikes                                           | 34 |

| 3.2 | Correction probability of memory reliability techniques for 22 |    |

|     | MeV particle strikes                                           | 35 |

| 3.3 | Memory Space (bits) of memory reliability techniques function  |    |

|     | of data size                                                   | 35 |

| 3.4 | Memory Space Overhead of memory reliability techniques func-   |    |

|     | tion of data size                                              | 35 |

| 4.1 | Pattern Injection Square                                       | 42 |

| 4.2 | Pattern Flipping Probability for 40nm technology [49]          | 43 |

| 4.3 | MBU example                                                    | 46 |

| 5.1 | Performance Overhead due to memory Reliability techniques      | 64 |

| 5.2 | Memory Reliability Techniques Comparison                       | 67 |

| 5.3 | RETGc of memory reliability techniques function of data size   | 68 |

|     |                                                                |    |

# List of Abbreviations

| MBU    | Multiple Bit Upset                                           |  |

|--------|--------------------------------------------------------------|--|

| SBU    | Single Bit Upset                                             |  |

| SEU    | Single Event Upset                                           |  |

| SER    | Soft Error Rate                                              |  |

| VP     | Virtual Platform                                             |  |

| SECDED | ECDED Single Error Correction Double Error Detection         |  |

| DECTED | <b>DECTED</b> Double Error Correction Triple Error Detection |  |

| RTEG   | Reliability Technique Evaluation Grade                       |  |

| DMR    | Double Memory Redundancy                                     |  |

| TMR    | Touble Memory Redundancy                                     |  |

|        |                                                              |  |

## Chapter

## Introduction

hanks to manufacturing process and integration improvements, modern mobile and embedded systems are now able to execute complex applications and can implement advanced functionalities, such driver assistant systems in autonomous automotive, drones etc. System-on-chip (SoC) manufacturers are expecting to produce in the next coming years chips with thousands of processing elements, very large cache memories and variety of dedicated accelerators using sub-micron node technologies.

Consequently, future SoC architectures will be more and more complex and the resulting hardware architectures will have a particular impact on the energy consumption, robustness and reliability. The obtained improvement in performance will go with a reliability downgrade due to the hardware integration rate increase. In [29] it has been proved that the error rate increases by a factor of  $\sqrt{2}$ , i.e. an increase of 40%, every 18 months due to node technology reductions. Transistor-node size shrinking combined with voltage reduction, create the need to tackle soft errors caused by transient faults. This type of faults is due to environment factors, such temperature and radiations, and corrupts data in memory and combinational units.

For this reason, next generation embedded systems have to be more resilient to transient faults than before. Robustness against transient faults, is for example, a standard requirement for safety-critical applications such as autonomous driving systems. Consequently, a large number of works have been devoted to study the impact of transient faults caused by energy particles striking in systems running safety critical applications. A large set of software and hardware solutions have been proposed to detect and eventually correct the resulting faults. Space and time redundancy solutions, such as Triple Modular Redundancy (TMR) combined with a voting system, have been widely used to support Single Event Upset (SEU).

Critical systems are system that needs to be highly reliable even after evolution, a failure of a critical system may have dramatic consequences for environment, financial or human lifes. However, in most of the existing approaches real environmental factors are not take into account and they assume only single faults. The rise of Multiple-Bit Upset (MBU) in nanometer technologies-based SoC, creates the need of simulation tools to explore their effect on system reliability. Indeed, solutions proposed to fight against single faults may be not appropriate to fight againt MBU. Moreover, systems complexity is rising even for critical systems. Thus a modification of the system is more and more expensive as the system advances in its development lifetime.

In this thesis, we will present our memory reliability techniques. Our technique called DPSR for double parity single redundancy is designed to answer specifically MBU while keeping a good trade-off between different criteria: computation overhead, memory area consumption, correction and detection probability, and integration complexity. To ensure our technique to bring an improvement to the state of the art, we have compared our approach to existing memory reliability techniques regarding the same criteria. To realize this study we have used our methodology of fault injection using a virtual platform. Our fault injection methodology takes into account environmental conditions, MBU and application behavior to inject realisitic faults.

The plan of the thesis is the following. In Chapter 2 we expose a state of

the art arround fault injection techniques and reliability enhancement techniques. To do so, we define fault types, we present a probabilistic model used in litterature and we explain fault consequences using a code example. We then define fault injection mechanisms and present some fault injection methodologies while focusing more onto simulation based fault injection. We then exposed different path of thinking about reliability enhancement techniques while focusing more onto memory reliability techniques.

In Chapter 3, we present and motive our memory reliability technique called DPSR. We then use a mathematical approach to validate our hopes about our proposition. This technique is proposed to answer a lack of reliability techniques designed to answer specifically MBU patterns and to fullfill a lack of memory reliability techniques designed to answer specifically MBU. This section ends by a presentation of a proposed global criteria, the reliability evaluation technique grade (RETG) to evaluated reliability techniques.

In Chapter 4, we expose our fault injector. We explain first our global way of thinking and then we detailled: how the application behavior is taken into account, how MBU are considered in our model, and how works our global algorithm. We end this Chapter by presenting the other injection mode that can be used while using our fault injection tool and why they are interesting.

Chapter 5 is the sum-up of our work, in this Chapter the goal is to use our fault injection methodology to evaluated reliability techniques. To do so, we firstly present our experimental setup. We then first evaluate our injection tool itself looking at efficiency, representativeness and overhead induced by the addition of the fault injector. In a third time, we ensure our mathematical approach to be validated by real experiments and we finally obtained the computation overhead induced by the memory reliability techniques. We end this Chapter by computing the global criteria RETG for our DPSR techniques and compare it to state of the art techniques.

Finally we conclude our work by resuming all our propositions to the

state of art but also by proposing evolution of our fault injection methodology but also to DPSR.

# Chapter 2

# State of the Art

| 2.1 | Fault  | Types                                                | 6  |

|-----|--------|------------------------------------------------------|----|

|     | 2.1.1  | Multiple Bit Upsets                                  | 8  |

|     | 2.1.2  | Probabilistic Model                                  | 10 |

|     | 2.1.3  | Fault Consequences                                   | 12 |

| 2.2 | Fault  | Injection Techniques                                 | 14 |

|     | 2.2.1  | Fault Injection Overview                             | 15 |

|     | 2.2.2  | Simulation-Based Fault Injection                     | 17 |

| 2.3 | Reliab | vility Techniques and Means                          | 19 |

|     | 2.3.1  | Global View of Reliability Enchancement Techniques . | 20 |

|     | 2.3.2  | Global Memory Reliability Techniques                 | 22 |

In this Chapter, we will first give basic definitions. We will then survey existing methods to model and simulate single and multiple bit upset in SoC. We will also present existing methods to improve system reliability. In the first part we expose and define what is a fault (Section 2.1), in the same part we talk also about Multiple Bit Upsets (MBU). Section 2.2 exposes fault injection techniques at different levels with a zoom made onto simulation based fault injection. We end this section with a presentation of different ways to protect the system against faults focusing onto memory reliability techniques in Section 2.3.

## 2.1 Fault Types

When functioning, embedded systems are subject to two kinds of faults. The distinction of those faults is made upon its duration. The two types are the following [50], [1]:

- 1. **Permanent Fault**. Permanent faults are caused by an undesired short or open circuit. When permanent faults appear, they are in place for the rest of the system life. For this reason, they are corrected by realizing a maintenance of the Hardware. This maintenance may be a component replacement or a soft/hard reset of the system. Due to functioning or fabrication issues, permanent fault occur mainly due to three different causes [7], [50], [47]:

- Manufacturing and Design Time: these faults comes from error in the design or in the manufacturing process of the Hardware and manifest as stuck at one or zero and delay.

- Wearout Mechanisms: these mechanisms are influenced by the aging of the system. Negative-Bias temperature instability, hot carrier injection, time-Dependent dielectric breakdown and electromigration are some of the mechanisms that produce this kind of faults. All cited mechanisms induce at the beginning intermittent faults that become permanent faults.

- Process Variations: The manufacturing induces a lot of process variability such as a non perfect doping for example. This randomness causes differences between transistors of the same chip. Differences of behavior for the same chip can be the reason for delays and thus alterate the behavior of the system.

- 2. Transient Fault. Transient faults are logical faults in circuit's operation and they occur at random mainly due to charged particle emissions [31]. Transient faults are non-permanent faults. The system is only perturbed during a small amount of time. The time of the perturbation is in general considered to be an instruction execution time at the application level. This reduction can be explained by the fact that transient faults are due to particle strike and thus happen for a very short moment even if the fault can stay for longer. The fault is materialized by one or more bit flips or a flip-flop modification. This change is called a single event and can cause a single or a multiple upset. The metric used to evaluate the sensitivity of the system to its environment is the soft error rate (SER) [30]. The SER is of course influenced by the type of particle encountered in the environment. At the ground level, there are three kinds of particles that are able to modify the state of a system. First, alpha particle is the most type of encountered particles. Second and third are the atmospheric neutrons that are usually separated in two categories based on their energy. More present, atmospheric neutrons with an energy inferior to 1 MeV and finally the atmospheric neutrons with an energy superior to 1 MeV. In the space environment, it exists different radiation sources such as: Van Allen radiations, solar activity and cosmic radiations [55]. Energies of these cosmic particles vary between some MeV and up to  $10^{30}$ .

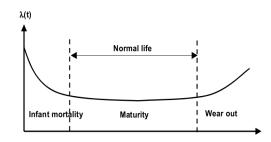

These two types of faults induce a failure rate for the entire system. Figure 2.1 extracted from [21] shows the evolution of the failure rate among three major steps of a system. In the first period the infant mortality, the system has a higher failure rate due to permanent fault high presence especially stuck at and process variations faults. Then the system enter in its maturity period where the system spends the main part of its lifetime. In this life period, the failure rate is almost constant and is mainly due to transient faults. Finally, the system enters in its wear out period, in this period the aging of the system makes the failure rate to increase. We add to transient errors permanent faults due to wearout mechanisms, this period is irreversible, only maintenance is able to reduce the failure rate rise.

FIGURE 2.1: Failure Rate Evolution During Life Periods For An Electrical System [21]

The main focus of our study concerns transient faults and thus we make the assumption our system is in its maturity life period. SER determines the number of soft errors per unit time. SER unit is the FIT, one FIT rates the number of failures expected for a device during one billion functioning hours. FIT is used mainly into the semiconductor industry. An accurate SER is obtained by measuring number of failures in devices operated in real uses conditions. It necessitates a large number of devices and also specific installation. A large number of guidelines to measure the SER are provided in the JEITA soft error rate testing guideline [20]. SER can also be measured during accelerated conditions using raditation sources such as thermal neutron, high energy neutron or alpha particle exposure.

#### 2.1.1 Multiple Bit Upsets

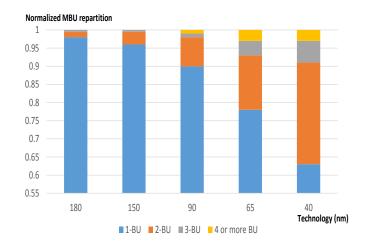

With the aim to maintain the Moore law prediction with the reality [43], transistor size has been reduced. This shrink has a direct impact onto the sensitivity of Hardware to single upset with the apparition and the raise of multiple faults observed for newest technologies. One of the first paper talking about MBU in SRAMs is [53]. The phenomena of MBU has been noticed above certain thresholds and due to strong constants such as high resistance. This phenomena of MBU is highlighted once again for SRAMs in [19] which shows that transistor miniaturization goes with the rise of single event multiple bit upset presence.

FIGURE 2.2: Single and Multi Bit Upset (BU) percentages by technology nodes in nm for SRAMs [19]

Figure 2.2 shows the growing presence of multiple bit upsets patterns. For example, in SRAMs under 40nm, more than 40% of particle strikes result in multiple bit upsets [19]. Usually, single event were linked to a single upset. With the rise of multiple upsets, Figure 2.2 shows that this hypothesis is valid only only for previous technologies. Results exposed in Figure 2.2 are obtained thanks to a neutron beam representing cosmic neutron flux at  $10^8$  the intensity of what is observed at the earth surface. Such as explained in the previous part, accelerated test are necessary to obtain results quickly than a simple exposure to a classical environment.

In Table 2.1, we present results obtained by Radaelli et al. [49] regarding the distribution of soft errors in 150nm commercial available SRAMs. The second line of the table is linked to the Table 4.1. For example, a 1-2 configuration corresponds to all upsets where two horizontally adjacent bits are flipped. Even if the study has been realised onto 150nm SRAMs, results are valid for future generations. Recent data are complex to obtain due to the cost of the facilities needed to obtain those results. This table shows that for

| Energy  | Double-bit pattern |     |     |        |

|---------|--------------------|-----|-----|--------|

|         | 1-2                | 1-4 | 1-5 | Others |

| 22 MeV  | 773                | 136 | 80  | 11     |

| 47 MeV  | 681                | 180 | 117 | 22     |

| 95 MeV  | 653                | 192 | 132 | 23     |

| 144 MeV | 686                | 156 | 133 | 25     |

| TABLE 2.1: Cumulative 2-Bit Event Count Normalized to 1000  |

|-------------------------------------------------------------|

| for 150nm SRAMs for Different Particle Strikes Energy (MeV) |

| [49]                                                        |

TABLE 2.2: Pattern Injection Square

| 1 | 2 | 3 |

|---|---|---|

| 4 | 5 | 6 |

| 7 | 8 | 9 |

single event 2-bit upsets, it is more frequent to observe two horizontally adjacent flips than two vertically adjacent ones. Multi-cell upset events tend to be a concern especially for patterns that flip multiple bits in the same row [19].

Even though a large sets of these results have been observed while the memory has been studied in static mode, the work presented in [54] shows the trend of MBU is also cocerning for the reliability of memory working into a dynamic mode.

As explained in [19], SRAM multi-cell upsets are much more common in newer technology nodes, and microprocessor designs need to be protected against them. To do so, probabilistic model are proposed and will be explained in the next Section.

## 2.1.2 Probabilistic Model

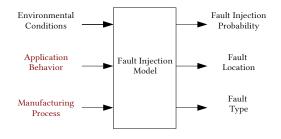

Even though the bit SER saturates or even decreases for latest technologies, the SER of the system is exponentially growing due to the high level of integration [12]. It is thus mandatory to consider soft errors during the development of a critical system. To be able to study soft errors, a probabilistic model can be used. A probabilistic model is a mathematical model allowing exploration tools to take into account faults. It can take into account different inputs such as environmental values, applications technology, manufacturing processes. In our work we focused our study on soft errors impacting memory. Such as previously explained in Introduction, we have decided to focus on the memory as it represents more than 80% of electronic components area. Nevertheless, all the study can be muted to study other hardware parts of the system.

First, depending on the impacted memory region, the flip operation may alter either a data value or an instruction code, but this difference between data or instruction alteration is not taken into account when creating the fault appearance probabilistic model. The reliability law is given by Equations (2.1) and 2.2, where  $\lambda$  is the constant failure rate, *R* is the reliability distribution, *MTTF* is the mean time to failure and *t* is the time.

$$R(t) = \exp(-\lambda * t) \tag{2.1}$$

$$MTTF = 1/\lambda \tag{2.2}$$

This model is based on a prior evaluation of the system failure rate and does not depend on system environmental conditions. Evolution of the fault model have been proposed in [28] and [57] who considered environmental conditions. In [28], failure rates are defined based on temperature while in [57], authors take power consumption into account. FIDES global electronic reliability engineering methodology guide is a generic approach to compute architectures failure rates [21]. Based on FIDES guide [21], physical and process impacts have to be considered for a precise failure rate  $\lambda$  computation. FIDES work is a sum up of what can be found in the literature regarding all criteria impacting the environment impact onto the failure rate. To compute the physical impact on  $\lambda$ , environmental conditions are modeled by providing: ambient temperature, temperature cycles, relative humidity, vibrations, saline pollution, environmental pollution, application pollution and chemical protection. Equations 2.3, 2.4 and 2.5 respectively respresent the Acceleration Factor of Temperature, Humidity and Vibrations. Thoses factors are used in the reliability evaluation of a system and can be positive or negative. These acceleration factor are most of the time forgetten when talking about electronics reliability and thus impact the probabilistic model drastically.

$$AF_{temperature} = exp(\frac{Ea}{Kb}(\frac{1}{T_0} - \frac{1}{T}))$$

(2.3)

$$AF_{humidity} = \left(\frac{H}{H_0}\right)^p * exp(11604 * Ea * \frac{1}{T_0 + 273} - \frac{1}{T + 273})$$

(2.4)

$$AF_{vibrations} = \left(\frac{G_{RMS}}{G_{RMS0}}\right)^p \tag{2.5}$$

In Equations 2.3, 2.4 and 2.5:

- *Ea* is the Activation Energy

- *T*<sub>0</sub> is the reference temperature in which the base failure rate has been computed, usually 20° C.

- *T* is the temperature of the environment

- *Kb* is the Boltzmann Constant =  $8.617.10^{-5} eV/K$

- *H* is the relative humidity of the environment

- *H*<sup>0</sup> is the reference relative humidity in which the base failure rate has been computed, usually 70%

- *p* is the power of acceleration for each factor.

- *G<sub>RMS</sub>* is the efficient vibration.

- $G_{RMS0}$  is the reference vibration, usually =  $0.5G_{RMS}$

The presented probabilistic model can be used in different processes to evaluate system reliability at different stages of the system development lifecycle. In particular, the presented fault probabilistic model is a base of our fault model presented later in the thesis. Indeed, it helps us to compute a fault probability for the entire system and we have adapted this fault probability to our needs. Our fault model will be exposed in the Section **4**.

#### 2.1.3 Fault Consequences

To illustrate the subject, I will use an example code available in Table 2.3 that describes a factorial computation of a number n defined before the compilation phase of the application. This application is smally protected by the

if statement at the line 9 which checks if the variable result is still superior to 0. Indeed, the result of a factorial is strictly superior to 0, this test is thus never wrong unless there is an exterior intervention. In a case of an exterior intervention, the result returned is -1 which corresponds basically to an error signal send to the caller of the function. Using this application, I will give example of different outputs that are possible after a fault occurence. Once the fault happens, different outputs are possible for the application:

- Silent Corruption: In this case, the fault has impacted the hardware but has no impact on the executed task. For the given example code it can be a fault that impact the value i while the return call is done. This will have no impact on the application and the fault will be masked as the variable i is a variable of the called function.

- 2. Detected Corruption: In this case, the fault is detected by the system. The fault is thus seen at the system level. Actions that can be taken by the system are: pointing out the fault, correcting the fault, restarting the current routine, etc. In our example in Table 2.3, the fault can be detected line 9. Let's suppose the fault changes the value of the variable "result" and set it to 0 during the for loop. Then the instruction at the line 9 will detect this modification. The factorial function will thus return -1. This value returned by the factorial function can be interpreted by the caller of the function as an error result.

- 3. Result Corruption: In this case, the fault is not detected by the system but changes the output of the system. In our example Table 2.3, imagine the fault happening onto the result variable during the for loop and not making the value of result to be inferior to 0. Then the fault will not be detected and the result will be false. The false result is finally send to the caller and nothing is raised by called to alert the caller of a possible error.

- 4. Behavioral Corruption: In this case, the fault is not detected by the system but changes the behavior of the system. In our example Table 2.3, if the fault happens onto the code that increments the i value (ligne 7) then the for loop is infinite and the function factorial would never end.

TABLE 2.3: Code Example 1

```

1. # define n 15

2. int factorial (void)

3. {

4.

int i, result;

5.

i = 2;

6.

result = 1;

7.

for (i=2; i<=n; i++)

8.

ł

9.

if(result > 0)

10.

ł

11.

result = result*i;

12.

}

13.

else

14.

{

15.

return -1;

16.

}

17.

}

18.

return result;

19. }

```

It causes the system to be blocked into an infinite loop. In this particular case, the beahvior of the entire system is impacted and stuck inside a loop.

# 2.2 Fault Injection Techniques

Fault Injection has been studied since decades now. Up to our knowledge, the first paper dates of 1967 [26]. Nowadays, fault injection is used at different levels and for different applications such as Operating System, Smart Card, Web services, etc. There are three different objectives when realising a fault injection campaign. First, ensuring the correct functioning of error detection and correction mechanisms. Second, evaluating the overall robustness of the system [47]. Finally, reducing the risk to discover unexpected scenario after the commercialization of the product.

# 2.2.1 Fault Injection Overview

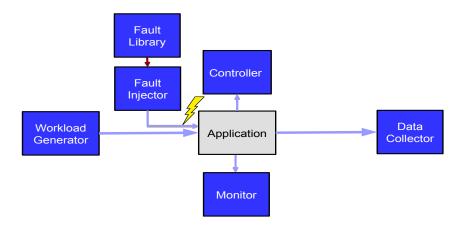

All fault injection environments are usually composed by the following components [38]:

- 1. Fault injector that modifies the system current state.

- 2. Fault library that stores different fault types, fault locations, fault times, and appropriate hardware semantics or software structures.

- 3. Workload generator which generates and stores different workload with different data input.

- 4. Controller and monitor, that control and track the injection target.

- 5. Data collector and analyzer which perform data collection, analysis and processing.

FIGURE 2.3: Representation of Fault Injection Environment

The components just presented and exposed in Figure 2.3 vary in complexity regarding the type of fault injection technique used. Indeed, existing fault injection techniques can be classified in four major types:

Hardware Fault Injection: In this technique external equipment is used to introduce faults into the hardware. We can cite laser for the Smart Card testing. We can also cite the recent work made onto the use of X-Ray in [5], which improves the injection by laser by making possible to target a transistor precisely. This technique is only usable in middle and late design phases as the software must run onto the chosen hardware to be able to run experiments. This technique has the advantage to be extremely representative of what can happen in a real system. However, targeting a special scenario becomes harder and harder as the technology evolves. In [5] on 60nm technology, the tool used to target specific transistor is pretty hard to set-up and need a specific facilities; it causes also a huge rise in price.

- 2. Virtual platform or Simulation-based Fault Injection: When used, this technique imposes to dedicate time to develop a simulation tool representative of the desired hardware [37]. Once the simulator available, the Fault injection can be applied at different levels:from transistor up to algorithm level depending on the abstraction level of the simulator. The main advantages of this solution is the early access of the testing procedure and the possibility to test during different development phases or scenario. It allows to target easily time and location of the injection. Main drawbacks are the simulation time that can be long if the system is fully simulated and the time needed to develop the simulator.

- 3. Emulation-based Fault Injection: The purpose is to rise the match between the simulated hardware and the real one while maintaining a decent testing time. This approach requires however more design time. Field Programmable Gate Arrays (FPGA) are most of the time used in this approach to represent the future hardware and the injection is realised thanks to software modules. The main advantage is the correlation between the simulation engine and the future hardware and the speed-up compared to Virtual platform low level. The drawback is of course the time used to develop the emulator and the time consumed by the update needed during the development of the product.

- 4. Software Fault Injection: this technique injects fault in the running software either during the debugging phase or by adding source code [38]. The lack of hardware behavior consideration is the major drawback of this technique as it is not representative of the final system. Furthermore, the final software is modified to allow the injection, when tested, the real software is not really tested because modified. This

| Fault Injection | Development Time | Fault Representativeness | Repeatable | Speed      |

|-----------------|------------------|--------------------------|------------|------------|

| Hardware        | High             | High                     | Hard       | Slow       |

| VP, Simulation  | High             | Medium                   | Easy       | Quick      |

| Emulation Based | Medium           | Medium                   | Easy       | Very Quick |

| Software        | Short            | Small                    | Easy       | Very Quick |

TABLE 2.4: Fault Injection Methodologies comparison

modification imposes a careful verification when removing the added code to ensure the system remaining reliable. During certifications processes, the final system is evaluated and issues may happen when the code furnished is not the tested one.

Table 2.4 is a resume of pros and cons of different fault injection presented just above. In our work we have only considered Fault Injection by Virtual Platform. This technique has been imposed to us due to research constraints but has major advantages such as the repetability of operations. We have tried to reduce the medium representativennes by improving the probabilistic model. The hardware fault injection is almost never done in real environemental conditions and is most of the time accelerated to gain money and time. A comparison of our obtained results may be a good follow-up to our presented work.

## 2.2.2 Simulation-Based Fault Injection

In this work, we focus on virtual platform-based fault injection. This group of fault injection technique can be split in two different approaches:

- 1. **Deterministic fault injection:** The fault injection is directly processed by the designer. Hence, all characteristics of injection are provided by the designer to the fault injector. Indeed, the fault library in this case is replaced by critical scenarios. This method is used to focus the analysis onto a critic code part or instruction of the application. It is also used to replay a scenario that have been proved to exacerbate issues when the non deterministic fault injection find the scenario.

- 2. Non Deterministic Fault Injection: This injection mode can be either applied at run-time [2] or at compile-time. If applied at compile-time,

faults are injected in the target hardware or in the executed code. This procedure is more used to test a given scenario that have raised concerns regarding the system reliability. The non deterministic characteristic of this injection comes from the impossibility to know before the run of the system the time and the location of the fault. Indeed, time, location and type of fault are determined by a probabilistic model. At run-time, the fault injection type, instant and location are determined by the *Fault Library*. This technique is more used to test the system as an entire entity and to evaluate the system reliability in its environmental conditions. It serves also to discover problematic scenario unexpected.

One of the main challenge about simulation is to select the correct level of abstraction [10]. Indeed, determining the correct level of abstraction refers to selecting the quantum of information included in the model to answer questions asked. There exist different abstraction levels for simulation which are [22]: High System level, Transaction level, Timed Transactional level, Register-Transfer level, Gate level and Transistor level. Historically the simulation was at the same abstraction level for all components but this limitation has been overpassed to allow users to determine abstraction level of different part of the simulated system. Indeed, each part of the system is considered has a black box and is connected to other system components by communications protocols. In conclusion, the abstraction level can be fixed for the entire simulated system or can be mixed regarding the level of precision needed. If we want to ensure the correct functioning of an application on a platform without performance limitation a high level of abstraction is valid, however if a precise performance measurement is needed, then the abstraction level must be as close as possible of the transistor abstraction level. The process of reducing the abstraction used decreases the simulation performance and thus takes more time to complete. It is thus important to balance the need of precision with the time allowed to the simulation step. Table 2.5presents a comparison of existing and commonly used fault injection tools. The fault injection tools presented are usually associated with different way to determine the injection type, location and its probability. J-Swift [51] and Ferrari [35] are examples of tool that proposes fault injection to evaluate system robustness. However, up to our knowledge, only one work has included

| Simulator Name                                             | Injection Level                                   | Determinism                                    | MBU                                    |

|------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|----------------------------------------|

| LEON3 Simula-<br>tor [2]                                   | architecture                                      | random                                         | yes                                    |

| FERRARI [35]<br>J-SWIFT[51]<br>BITFIT [40]<br>SASSIFI [27] | software<br>software<br>prototype<br>control flow | free choice<br>random<br>model-based<br>random | possible<br>possible<br>possible<br>no |

TABLE 2.5: Comparison of Fault Injection Tools

multiple bit upsets in their injection fault library [2]. This work has been made for LEON3 architecture. The authors use random fault injection in time and in memory location.

# 2.3 Reliability Techniques and Means

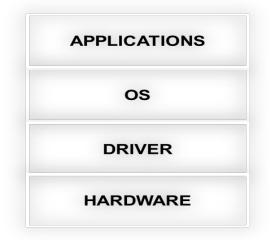

A classical system representation is given with four layers. Figure 2.4 shows the four classical layers of a system. The hardware is explicit and contains all chips, connexions, I/O from the physical point of view. The Driver layer is set up upon and is the link between the hardware and the Operating System. The Operating System is the layer allowing the Application layer to work correctly onto its hardware, it also handles the memory management and the scheduling of application. Finally the Application layer is the layer that makes the job wanted by the user. It contains mainly the visble part of the iceberg.

FIGURE 2.4: Representation of a System

To protect systems against MBU, reliability techniques and means are used at different levels of the system. Reliability techniques have different goals when implemented which are [37]:

- 1. Prevention: avoiding the fault to occur on the system.

- 2. Tolerance: prevent failures when faults are present in the system

- 3. Correction: prevent failures by correct faults before propagation

- 4. Forecasting: evaluate the system behavior and comparing it to faulted behavior. The goal is to determine if the technique reaches expected results of Prevention, Detection and/or Correction.

#### 2.3.1 Global View of Reliability Enchancement Techniques

As the system is composed of different layers, it exists reliability techniques for every layers. It exists excellent survey talking about this subject and grouping a lot of reliability techniques such as [42].

One of the main concept associated to reliability is redundancy. Redundancy is the fact to multiply an instruction, a function, a storage or even a component to be able to compare information obtained by different object and compare them together to be able to detect a fault.

In the work presented in [52], authors duplicates L1 caches to be able to detect if an error occur. The methodology is especially efficient to raise reliability as L1 caches are highly accessed, they are more subject to propagate faults. To tackle the problem, they duplicate caches. With the same spirit, the work [56] duplicates information in the L1 cache in the same cache but at two different places. In this work, they use dead cache block (block not used for a long time) to hold replications of newly cache stored information. This technique is more efficient than the previous one as less memory impacting but is usable only when cache is not fully used. In those presented works, only detection is faisible as variables are only stored twice in memory, it becomes thus impossible to determine which caches has been impacted. In the work presented in **??**, authors propose to chose between a double or a triple cache redundancy. If the double redundancy is used, only detection is possible, in the case of a triple redundancy, the correction is possible by voting

for the more present value. The redundancy is also used during scheduling. Works like [18] and [24] uses the parallelism of multi cores application to replicate certains functions or certain functions parts in other cores and compare results at the end to determine if a fault has occured. Those techniques have been optimized in [32] where replications of tasks is not static but dynamic and are induced by different mechanisms such as a result checker and time/memory usage valdiation. Indeed, using two cores to compute the same set of instructions is not efficient. Moreover, most of critical systems developped onto multi cores platforms are linked with static scheduling. This staticness is due to constraints of worst case execution time ordered by critical systems. It is far more complicated to ensure worst case execution time matching with a dynamic scheduling than with a dynamic one.

Another main concept associated to reliability is separation. Separation consists in spliting information to reduce the risk that a fault affects the meaningfull information. In the work [23], they cut the meaningfull information in two parts. The first part is stored followed by 0 and the second part is stored preceded with 1. In a case of a fault, the probability is divided by two to modify the meaningfull value. However, two lines in memory are subjects to fault, this modification raise the probability of a transient faults to happen but is negligible compared to the gain in reliability for the system.

Another concept associated to reliability is called write back. Write back consists in writing data in another memory section after a certain amount of time. Works like [6], [41] stored data from L1 cache to other place (Mainly in other Cache Levels, sometimes in global memory) after a certain amount of time. The time where information is written back is determined by a number of clock cycles.

All those reliability enhancement techniques are set at different layers of the system. An emerging idea is to combine those different techniques by taking best advantages of all of them to raise the reliability in different situations while maintening a good level of speed, memory overhead and power consumption. An impressive work has been realised during the CLEAR project [17], in which authors compare cross layer reliability techniques together. Techniques have been applied at diffeWith the previsouly part regarding Multiple Bit Upsets, we shown their assumption to be less and less true with the improvement in manufacturing process and an evolution of their work would be to consider MBU.

Finally, in the next section, we focus onto memory reliability techniques as memory represent more than 80% of electronic area and is thus more sensible to particle strike. We will give an overview of global concepts and ECC (error correcting code) to protect memory.

### 2.3.2 Global Memory Reliability Techniques

We present now some memory reliability techniques used to fight against single and multiple upsets that we want to study all along our work. Some techniques used to fight against single upsets are still used nowadays. In all figures for this part, b0 represents the bit 0 of the work (thus the most significant bit or the less significant bit).

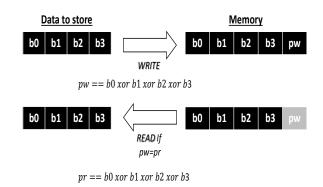

- Parity. This technique consists in adding a bit to the memory line or column to compute the number of 1 or 0 stored in the line or the column. As shown in Figure 2.5, during the write operation, a XOR operation is realized between all bits to store and the result is added to the stored bits. This technique detects all single bit upsets but cannot determine the position of the corrupted bit in memory. The correction of the error is thus not possible.

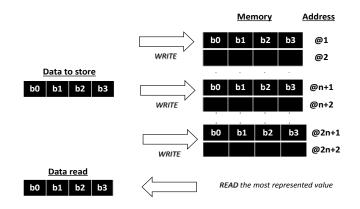

- 2. Double and Triple Memory Redundancy (DMR/TMR). As shown in Figure 2.6 DMR/TMR techniques consist in doubling or tripling the data that is stored. In the case of the double respectively triple redundancy, the data is stored twice respectively three times in memory. Memory areas where data are stored have to be separated enough to consider a particle strike modifying only one stored version. DMR does not allow to correct the value perturbed as it is impossible to know the value modified. The triple redundancy however allows to determine

FIGURE 2.5: Parity Functioning

the line that has been perturbed. Indeed, the value is stored three times in memory during the write operation. During the read operation, a voter is associated to decide the correct value between the three proposed and the majority determines the real value. With the hypothesis of the gap sufficiently big between redundant memory areas, the DMR allows to detect all kinds of errors and the TMR allows to detect and correct all kinds of errors. The main disadvantage of this memory technique is its memory space usage.

FIGURE 2.6: TMR Functioning

With the same spirit, solutions have been developed to address specific need of robustness by replicating different parts of the hardware such as column, row or even part of the memory. However those solutions are more used to protect against manufacturing errors and not against soft errors. In addition, those solutions goes with a rise in cost and complexity as sometimes a single erroneous bit make an entire part of the memory unusable. With process variations increase, the solution seems to reach its limits [46], [44].

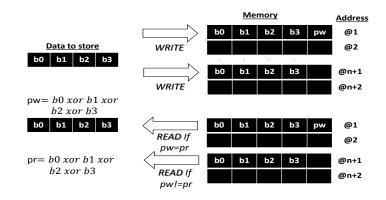

3. **Parity-Based Mono-Copy Cache (PmC2)**. In [4], authors propose to combine the double memory redundancy and the parity to create the PmC2 technique. Such as shown Figure 2.7 In this technique, during write operations, the parity bit is used and associated with a redundancy procedure to store the data in another memory location. During the read operation, the parity bit of the value read is compared to the parity bit stored, if there is a difference, the value taken is the one stored redundantly. This technique is a trade-off between single parity bit and the TMR, it uses the power of detection of the parity bit and use the redundancy to correct the fault once detected.

FIGURE 2.7: PmC2 Functioning

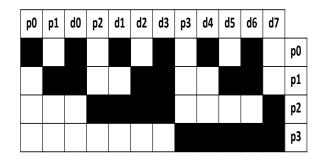

#### 4. Single Error Correction Double Error Detection

(SECDED). Even if it exists optimized versions of the Single Error Correction Double Error Detection mechanisms [48] the principle stays the same for all implementations. We base our study on SECDED codes based on Hamming codes. As shown Figure 2.8 the SECDED protection can be seen as an extension of the parity bit allowing to detect double error and correct single error. Data word represented by *bx* bits are protected by adding extra information represented by the *px* bits. Equations 2.6, 2.7, 2.8, 2.9, and 2.10 give an example of SECDED implementation for 8 bits data words. During the write operations, *px* bits are computed and stored together and mixed with all the *dx* bits. A last protection bit (called *p*4 Equation 2.10) is added that is a xor between

all the other *px* bits but is not represented in Figure 2.8. During the read operations, the same operations are done to ensure that the value protected have not been modified between the read and the write. This solution is expensive in terms of computation time, the main advantage of this technique is that it scales very well in terms of memory footprint when the data size to protect raises. Indeed, less and less bits are needed when the data size raise, for example, we need 2 bits to protect 2 bits but we only need, 5 bits to protect 16 bits. SECDED functionning is represented in 2.8, all black boxes are XOR operations realized between bits that give the value for the parity bit. When the data is read, all parity bits are once again computed and compared to previously stored ones. If it exists a difference, a fault has occured.

$$p0 = d0 \oplus d1 \oplus d3 \oplus d4 \oplus d6 \tag{2.6}$$

$$p1 = d0 \oplus d2 \oplus d3 \oplus d5 \oplus d6 \tag{2.7}$$

$$p2 = d1 \oplus d2 \oplus d3 \oplus d6 \tag{2.8}$$

$$p3 = d4 \oplus d5 \oplus d6 \oplus d7 \tag{2.9}$$

$$p4 = p0 \oplus p1 \oplus p2 \oplus p3 \tag{2.10}$$

FIGURE 2.8: SECDED example for 8 bits data word

# 5. Double Error Correction Triple Error Detection (DEC-TED)

First time published in the beginning of 1980s [16], this technique is now used in the critical system development industry. Indeed, such

as explained in the Section 2.1.1, the number of MBU presence is constantly rising with the reduction of transistor size. Thus, for systems needing a strong reliability aspect, they evolve from a SECDED error correcting code to a DEC-TED code. Far more complex to implement and thus more performance downgrading, this technique sets itself as an intermediate between the existing SECDED and the TMR. In our experiments, we implement the one proposed in [33] because of its widely usage. The extra data stored are separated in three categories and we are going to give an example for 32 bits data word to protect that induces 16 bits of protection:

- (a) The first group is composed by 7 bits evenly distributed. This group has the same power of correction and detection of SECDED (with more bits used).

- (b) The second group is composed by 8 bits similar to the first group, but in this case, 8 bits are used and those bits are computed differently from the first group. Due to this feature, the system is capable to detect triple error.

- (c) The final group is composed by a single bit that is the parity of the bit in the second group. It allows to detect single error that may happen onto check bits and thus reduce the number of false positive.

Even if the optimized number to double correct and triple detect faults is 11, this scenario in real implementations is far more realistic as it exists a granularity for memory and memory are most of the time composed by power 2 data storage capacity.

6. **Physical Bit Interleaving**. As multiple faults number increase, and the complexity of techniques used to fight against multiple faults will not stop to rise, the physical bit interleaving is a solution less complex. The principle of this solution is to interleave words together on the same line and thanks to this procedure, multiple faults on the same line are reduced to smaller multiple faults and thus less complex error correcting code are enough to correct errors. However, during a read, the

entire line is read and a operation has to be made to obtain the desired word. A table of corresponding position is stored in memory and two interleaved words has to be accessed at two different time. it is also more power consuming [36].

As we can identify here, solutions proposed to protect the memory are either not efficient against multiple bit upsets, either complex and thus time and energy consuming either hugely impacting the memory size that is unacceptable for embedded systems. In the next part, we propose a new memory reliability technique developed with awareness about multiple bit upsets and embedded systems constraints. We will follow this proposition with a new metric to compare reliability enhancement techniques.

# Chapter 3

# Double Parity bit Single Redundancy

| 3.1 | Presentation and Motivation                                  |                                         |    |  |  |  |  |

|-----|--------------------------------------------------------------|-----------------------------------------|----|--|--|--|--|

| 3.2 | Probabilistic comparison between existing memory reliability |                                         |    |  |  |  |  |

|     | techni                                                       | ques and DPSR                           | 32 |  |  |  |  |

|     | 3.2.1                                                        | Detection                               | 33 |  |  |  |  |

|     | 3.2.2                                                        | Correction                              | 34 |  |  |  |  |

|     | 3.2.3                                                        | Memory Space                            | 35 |  |  |  |  |

|     | 3.2.4                                                        | Discussion                              | 36 |  |  |  |  |

| 3.3 | RETG                                                         | Reliability Enhancement Technique Grade | 36 |  |  |  |  |

In this Chapter, we first present and motivate our proposition of a new memory reliability techniques called DPSR in Section 3.1. We then, mathematically analyze our techniques compared to other techniques presented in the previous Chapter. Section 3.2 presents the detection and the correction probability of our techniques compared to other ones, we also analyze the memory overhead of different memory reliability enhancements techniques. In Section 3.3 we present a global metric to compare with one metric memory reliability techniques.

## 3.1 Presentation and Motivation

As mentionned earlier, the phenomena of MBU is becoming more urgent with technology scaling down and the critical systems high performance requirements. Actually multiple bit upsets tend to be the major type of upsets observed [19]. Critical systems have to conserve their reliability level. To address the problem we propose a new memory reliability enhancement technique considering MBU patterns.

We provide the solution of a double parity bit associated with a simple redundancy. We call it DPSR (Double Parity Single Redundancy). DPSR has the objective to cope with most encountered MBU patterns. Contrary to different techniques considering multiple faults to be totally random, our technique takes into account MBU pattern probabilities. The particularity of multiple faults happening on memory is the proximity of flipped bits [19].

Regarding this particularity, we suggest to use two parity bits for the detection. Such as showed later in Section 3.2.1, the proposed technique detects more than 99.6% of encountered upsets. Adding a third bit would raise this percentage of 0.3% but appears hard to implement as most of memory are based on power 2 size. Using a fourth bit is enough to correct all patterns studied in our works and is conceivable but it also raises the memory area. This area rise is problematic as it makes particle strike on the system more frequently modifying the memory state. That explains why we decided to stick with only two parity bits. Finally as explained in [4], the parity bit is easy to set up. It can be done on different system layers and can be accelerated in different ways.

With the same spirit as what has been achieved in [4], we decide to add a redundancy for the word in a separate **non adjacent** memory location. This redundant storage will be useful for data recovery in case of a detected corruption. Hence, our technique deploys 2 bits to detect the fault and redundancy for error correction. It's worth noticing that depending on the required reliability, this technique can be used for detection only, or for detection and correction.

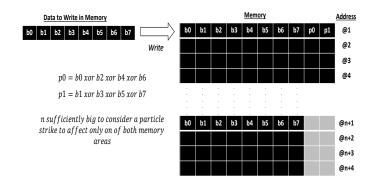

Figure 3.1 explains the functioning of the technique during a write operation in memory for an 8 bits word. When data is stored, two parity bits are computed. Equations 3.1 and 3.2 give the formula for the even and the odd parity bit in the case of an 8 bits word. Once both bits are computed, the word is stored twice in memory. They are not stored in adjacent addresses but rather in different memory locations. As shown in Figure 3.1, bits *po* and *p*1 correspond, respectively, to even and odd parity bits are stored within the original data.

During a read operation, as illustrated by Figure 3.2, the original is read. Even and odd parity bits are computed for the read value. The freshly computed even and odd parity bits are compared to stored even and odd parity bits. If they match, we consider the data to be fault free and the read operation carries on. In the case of a mismatch, the value or the parity bits has been corrupted. The read operations returns the redundant data.

The choice of interlaced bits to compute the two parity bits comes from the observation that it is very unlikely to find a 2 bit upsets that have a gap between the two flipped bits. Regarding the work [19] it is less than 2% for 2 bits upsets that make less than 0.6% of total observed patterns for 40nm SRAM technology. Moreover, in the case of a 3 bits upsets, the only pattern that may lead to corruption even with our solution is when three horizontally aligned bits are flipped. The chance to observe this pattern for a 3 bits upset is less than 0.28% that represents less than 0.028% of total observed upsets for 40nm SRAM technology. In the next parts, we compare with more details the proposed technique to other ones in presence of multiple bits upsets.

$$p0 = b0 \oplus b2 \oplus b4 \oplus b6 \tag{3.1}$$

$$p1 = b1 \oplus b3 \oplus b5 \oplus b7 \tag{3.2}$$

FIGURE 3.1: DPSR Write for 8 bits word

FIGURE 3.2: DPSR Read for 8 bits word

# 3.2 Probabilistic comparison between existing memory reliability techniques and DPSR

In this section we evaluate used memory reliability techniques and our technique against the data provided by [19] and exposed in the Section 2. The study of memory reliability techniques is made for different particle strikes energy. The choice of the implemented reliability technique depends on different parameters. Thus choosing a perfect reliability protection is pratically impossible.

Indeed, in the case of a multidimensional problem, it is almost impossible to maximize all parameters. The goal in multidimensional problems is to find solutions that are trade-off between all solutions. The choice of a memory reliability technique is crucial and has to be a trade-off between: detection, correction, memory space and speed of the reliability technique. In this probabilistic study, we evaluate the detection probability, the correction probability and the memory space used by the reliability technique chosen. The only hypothesis made is that faults can occur on every bits of the word, however even if the added data is faulted, the detection has to happen. The probabilistic model is based on Equation 3.3 and data used are from [19]. In Equation 3.3,  $p_{BU}$  and  $p_{shape}$  corresponds respectively to the probability to observe a 1, 2, 3 or 4 BU and to the shape of upsets to inject. They both depend on the memory technology and on the particle energy. Finally  $p_{fault}$  is the probability to observe a given fault pattern.

$p_{fault} = p_{BU}(technology, particle energy) * p_{shape}(technology, particle energy)$ (3.3)

### 3.2.1 Detection

The detection rate is the probability of a memory technique to detect a fault in a given environment. In this Section we compare the parity (that has the same detection rate as the PmC2 technique), with the classical DMR, SECDED techniques and with the DPSR. The detection probability  $p_{detection}$  is computed following Equation 3.4 where  $p_{detectionfault}$  equals 1 if the technique detects the type of fault else it is 0. We assume a single fault affecting only one memory area.

As shown in Table 3.1, all techniques have the same rate for detecting single faults. However, this rate goes down when multiple upsets appear.

|      | Parity | DMR | SECDED | DPSR  | DECTED |

|------|--------|-----|--------|-------|--------|

| 1BU  | 1      | 1   | 1      | 1     | 1      |

| 2BU  | 0.22   | 1   | 1      | 0.999 | 0.999  |

| 3BU  | 0.059  | 1   | 0.999  | 0.994 | 0.999  |

| 4BU  | 0.010  | 1   | 0.990  | 0.976 | 0.999  |

| Mean | 0.704  | 1   | 0.999  | 0.996 | 0.999  |

TABLE 3.1: Detection probability of memory reliability techniques for 22 MeV particle strikes

The DMR is the best technique to detect multiple faults due to its capacity to detect all kinds of faults, the DPSR that is our proposed technique is close to what SECDED and DMR propose for detection rate.

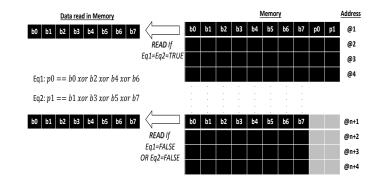

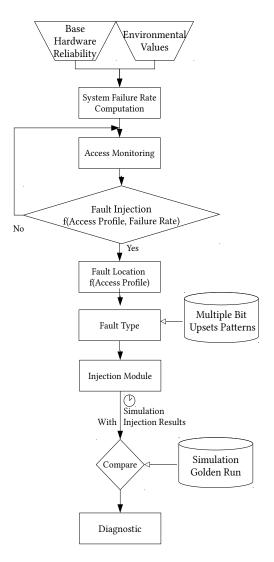

$$p_{detection} = \sum_{fault} (p_{fault} * p_{detectionfault})$$